Hauptlinks

Suchen

Hardware- und Nachrichten-Links des 19. April 2019

Laut Bits 'n' Chips sollen die Zen 2 Core-Dies in der 7nm-Fertigung von TSMC eine Produktionsausbeute von immerhin 70% aufweisen – was jetzt nicht ganz so gut ist wie bei Zen 1 (angeblich ~80%), aber dennoch eine sehr gute Zahl für ein neues Fertigungsverfahren darstellt. AMD kommt an dieser Stelle die kleine Größe des Core-Dies von Zen 2 (je nach Schätzung 73-88mm²) zu Gute, denn je größer die Chipfläche ist, um so geringer ist die relative Ausbeute bei einer gesetzten Anzahl an Fertigungsfehlern pro Wafer. Anders formuliert: Wäre Zen 2 ein monolithischer Chip von ~210mm² Chipfläche (wie bei Zen 1), wäre basierend auf derselben Anzahl an Fertigungsfehlern die Produktionsausbeute deutlich niedriger, bei geschätzt unter 30%. Und dies ist dann schon eher eine Größe, welche für ein neues Fertigungsverfahren (welches AMD auch noch vergleichsweise früh nutzt) bekannt ist. Ein weiterer Vorteil der kleinen Core-Dies ist dann, das mit der Konzentration jener Core-Dies rein auf CPU-Kerne samt Cache und Anbindung die Chance steigt, mit einem einzelnen Produktionsfehler nur einen Rechenkern oder Cache zu erwischen – womit das Core-Die teildeaktiviert trotzdem noch funktionsfähig und damit verkaufbar ist.

Bei einem monolithischen Prozessor steigt dagegen der relative Anteil der Chipteile, wo kein Fertigungsfehler passieren darf (Anbindung, I/O etc.), wo also im Fall des Falles das komplette Die dann wertlos wäre. Die Aufteilung von Zen 2 in Core-Dies (7nm TSMC) und I/O-Dies (14nm GlobalFoundries) steigert also nicht nur die originäre Produktionsausbeute durch vergleichsweise kleine Chipflächen, sondern ermöglicht auch noch eine höhere Rate an doch noch verwendbaren Dies im Falle eines Fertigungsfehlers. Hinzu kommt bekannterweise noch die hohe Flexibilität dieses Ansatzes, wodurch sich sehr einfach Prozessoren mit sehr vielen Rechenkernen bzw. für jedes Marktsegment Prozessoren mit der marktüblichen Anzahl an Rechenkernen sowie der passenden I/O-Einheit erstellen lassen. AMD scheint bezüglich all dieser Punkte erst einmal aufs (betriebswirtschaftlich) richtige Pferd gesetzt zu haben – wie man die Schwierigkeit eines performanten wie latenzarmen Speicherzugriffs bei mehreren Dies pro Prozessor löst, muß dagegen dann die Praxis zeigen.

Die PC Games Hardware verweist auf ein neues Reddit-Gerücht zur Playstation 5, nachdem die kommende Sony-Konsole angeblich über eine ungewohnte Speicheraufteilung verfügen soll: 8 GB HBM2 an einem 2048 Bit Speicherinterface sowie 16 GB DDR4 an einem 256 Bit Speicherinterface. Von diesem DDR4-Speicher sind 4 GB für das Betriebssystem reserviert, womit die Konsole dem Spieleentwickler insgesamt 20 GB Speicher offeriert – welche vom HBCC-Feature der Navi-Grafiklösung automatisch verwaltet werden. Dies hört sich erst einmal nicht besonders glaubwürdig an, weil es letztlich den Verbau von gleich zwei Speicherinterfaces im Konsolen-SoC erfordern würde – samt entsprechend größerer Chipfläche und höherem Stromverbrauch. Die Alternative mit einfach 24 oder 32 GB HBM2-Speicher erscheint da in jedem Fall eleganter – wobei es für Außenstehende natürlich nicht ermittelbar ist, in welche Richtung die Kosten-Kalkulation an dieser Stelle tendiert. Mehr als eine Außenseiter-Chance ist für diese Auflösung allerdings nicht zu sehen, denn der genannte Ansatz ist mit einem zusätzlichen QuadChannel-Speicherinterface und DDR4-Speicher (gemäß der angegebenen Bandbreite) auf gleich DDR4/4000 auch nicht gerade günstig.

Hinzu kommt, das im selben Gerücht auch noch von einem weiteren Refresh der (originalen) Playstation 4 gesprochen wird, bei welchem der Konsolen-SoC auf die 7nm-Fertigung von Samsung geschrumpft werden soll. Letzteres macht kaum noch einen Sinn, denn dadurch wird die bestehende Konsole mutmaßlich nicht wirklich günstiger (vielleicht beim Netzteil, aber kaum beim Konsolen-SoC). Vor allem aber ist zu bezweifeln, das von der originalen Playstation 4 überhaupt noch so große Stückzahlen abgesetzt werden können, auf das sich ein (nochmals) geschrumpfter Konsolen-SoC wirklich lohnt. Sony dürfte eher darauf bedacht sein, ab dem Jahr 2020 die Produktionsmengen zurückzufahren, um nicht irgendwann nach dem Release der Playstation 5 plötzlich noch zu hohe, nicht mehr absetzbare Lagerbestände der Altkonsole zu haben. Gänzlich unmöglich ist natürlich keines dieser Gerüchte – allerdings erscheinen beide als technisch deutlich zu ausgefeilt für Gerüchte-Informationen, welche üblicherweise durch einige Hände gegangen sind und daher zumeist nur grobe Stichwörte sowie oftmals nur unzusammenhängende Informationsbrocken liefern.

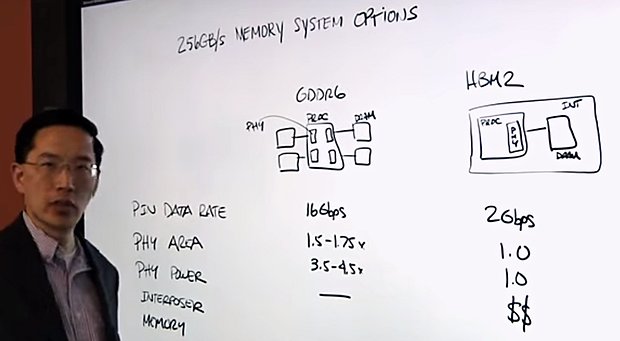

Passend hierzu gibt es bei Semiconductor Engineering ein Video, welches sich mit dem Vergleich von GDDR6 zu HBM2 beschäftigt. Dabei wurden auch ein paar schon bekannte, aber dato eher selten quantifizierte Unterschiede präzisiert: So ist bei gleicher insgesamt herauskommender Speicherbandbreite ein GDDR6-Speicherinterface immerhin 50-75% größer und verbraucht vor allem 3,5 bis 4,5mal soviel Energie. Letzteres ist wohl der Hauptgrund, wieso AMD schon früh auf diese Speichertechnologie gegangen ist: Alle AMD-Grafikchips der jüngeren bis mittleren Vergangenheit sind deutlich stromfressender als vergleichsweise nVidia-Grafikchips – womit diese Entlastung des Stromverbrauchs beim Speicherinterface um so interessanter für AMD ist. Aber auch nVidia hat bei den HPC-Chips GP100 und GV100 bekannterweise auf ein HBM2-Speicherinterface gesetzt – und auch dort dürfte das primäre Interesse dem Stromverbrauch gegolten haben, welches bei diesen Profi-Chips immer schon sehr hoch ist und was dort vor allem für Rechenaufgaben und eben weniger für das Speicherinterface genutzt werden soll.

Allerdings dürfte GDDR6 auch weiterhin den Vorzug erhalten, sofern es um gängig große Speicherinterfaces bzw. normalgroße Speicherbandbreiten handelt – wie die im Beispiel behandelten 256 GB/sec., was bei GDDR6 ein 128-Bit-Interface mit 4000 MHz QDR Speichertakt ergibt, bei HBM2 ein 1024-Bit-Interface mit 1000 MHz DDR Speichertakt. Hier ergeben die relativen Vorteile von HBM2 bei Platzbedarf und Stromverbrauch zu geringe absolute Vorteile und berühren vor allem keine feststehenden Grenzpunkte bei Chipfläche und maximalen Stromverbrauch – womit die Vorteile von GDDR6 in Form des deutlich günstigeren Speichers und der insgesamt einfacheren Realisierung (Verzicht auf extra Interposer, größere Verfügbarkeit, mehr Lieferanten) dann immer gewinnen werden. HBM2 ist vor allem dann eine Option, wenn es um sehr große Chips geht, wo man gern ein wenig Chipfläche bzw. Stromverbrauch einspart (welches man dann lieber für andere Sachen verbrät) bzw. wo entsprechende GDDR6-Speicherinterfaces dann einfach zu groß werden würden. Dies trifft sicherlich auf 512-Bit-Interfaces zu, welche bei GDDR6 sehr dick und sehr stromhungrig werden würden – in dieser Klasse (bei Bandbreiten ab 800 GB/sec) ist die Nutzung von HBM2-Speicher dann fast obligatorisch.