Hauptlinks

Suche

AMD Bulldozer: Rechenkerne in Modul-Bauweise

AMD hat auf der HotChips-Konferenz seine zwei neuen CPU-Architekturen Bulldozer und Bobcat nunmehr offiziell vorgestellt. Die entsprechende Präsentation gibt es beim Planet 3DNow! zu besichtigen, wobei in dieser jedoch nur wenige konkrete Fakten zu den beiden CPU-Architekturen genannt werden – diese hat AMD erst im Anschluß an die Präsentation bekanntgegeben. Für Aussagen zur konkreten Performance und zu den geplanten Taktfrequenzen ist es allerdings derzeit noch zu früh, dies dürfte jeweils erst kurz vor Launch bekanntwerden.

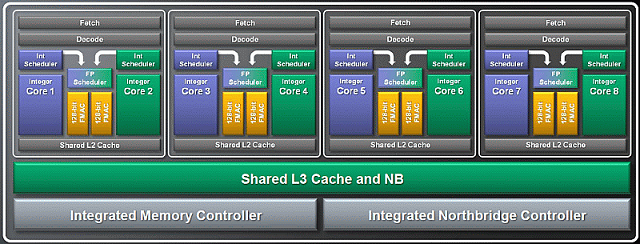

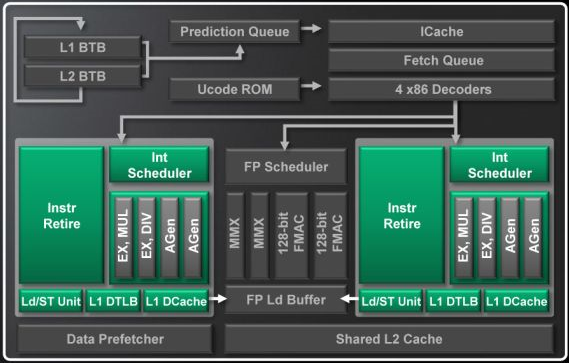

Allerdings sind gerade zu Bulldozer ein paar Details klarer geworden: So betrachtet AMD die zwei Integer-Recheneinheiten eines Bulldozer-Moduls als zwei regelrechte Rechenkerne, genauso dürften diese sich auch im Betriebssystem anmelden. Ein Vierkern-Prozessor der Bulldozer-Architektur besteht dann ergo aus zwei Bulldozer-Modulen, ein Achtkern-Prozessor aus vier Bulldozer-Modulen (so wie auf vorstehendem Bild) – und dies obwohl sich somit zwei Rechenkerne gewisse Teile der Pipeline und vor allem die Fließkomma-Einheit teilen (so wie auf nachstehendem Bild zu sehen).

Dies bedeutet, daß die einzelnen Bulldozer-Kerne im eigentlichen eine Vereinfachung gegen bisherigen AMD-Prozessoren sind – wobei für den Augenblick noch nicht ganz klar ist, was dies bringen soll. Sicherlich spart dies Chipfläche (die zweite Integer-Einheit kostet nur 12% mehr Transistoren), aber angesichts der relativ kleinen Chipfläche für die eigentliche Prozessorlogik und der großen Chipfläche für die umfangreichen Caches von Bulldozer bringt dies keinen beachtbaren Vorteil bei der insgesamten Chipfläche – vor allem nicht bei einer CPU, die nicht für LowCost-Gefilde gedacht ist und daher keinem so hohen Kostendruck ausgesetzt ist.

Einen direkten Performancevorteil hat das ganze System auch nicht, da gemäß AMD die Modul-Bauweise nur 80 Prozent der Performance einer gewöhnlichen DualCore-Bauweise mit zwei normalen Rechenkernen erreicht. Spöttisch könnte man das ganze als "HyperThreading+" bezeichnen, denn ähnlich wie HyperThreading nimmt es nur wenig Chipfläche weg (HyperThreading kostete 5% mehr Transistoren) und bringt natürlich nicht die volle Leistung von einem echten weiteren Rechenkern. Allerdings dürfte AMDs Modul-Ansatz eine wesentlich konstantere Mehrleistung als HyperThreading bringen, da bei AMD ein Großteil der Ausführungseinheiten doppelt vorliegt und bei HyperThreading faktisch nur die Register doppelt sind. Ob man allerdings ein Bulldozer-Modul wirklich als zwei vollwertige Rechenkerne ansehen soll, ist diskussionswürdig.

Bleibt weiterhin die Frage, wieso sich AMD zu dieser Modul-Bauweise entschieden hat, welche schließlich sogar etwas an Performance kostet. Wir können uns vorstellen, daß man es hierbei in erster Linie auf die Verlustleistung des Prozessors abgesehen hat, was indirekt dann wieder die Taktbarkeit beeinflußt. Da derzeit im Prozessoren-Bereich die Verlustleistung stark beachtet wird, können die Prozessorenentwickler nicht einfach neue Designs mit höherer Performance herausbringen, welche diese Mehrperformance nur unter einer entsprechend höheren Verlustleistung erreichen – gerade im Desktop-Bereich gilt es derzeit, die psychologisch wichtige Marke von 130 Watt Verlustleistung nicht zu überschreiten.

So gesehen ist dies ein guter Tausch, wenn AMD für 12 Prozent mehr Logik-Transistoren 80 Prozent mehr Performance herausholt – weil es ja auch nur 12 Prozent (oder etwas mehr) Verlustleistung bedeutet. AMD könnte es mit Bulldozer also endlich einmal hinbekommen, Intel auch bei der Frage der Verlustleistung wieder unter Druck zu setzen – und gerade die HighEnd-Modelle von Intel sind in dieser Frage schließlich nicht unangreifbar. Alternativ kann man die niedrigere Verlustleistung auch dazu ausnutzen, mit deutlich höheren Taktraten gegenüber Intel anzutreten.

Allerdings hat AMD die Integer-Einheiten der einzelnen Integer-Rechenkerne bei Bulldozer beschnitten: Die vorstehend dargestellten "vier Pipelines" ergeben nur zwei INT- und zwei AGU-Einheiten – und nicht vier INT- und vier AGU-Einheiten, wie vorab oftmals spekuliert bzw. erhofft (die INT-Einheiten sind die eigentlichen Recheneinheiten, die AGU-Einheiten dienen nur der Datenaddressierung). Wie AMD damit die dringend benötigte höhere Pro/MHz-Leistung bieten will, ist unklar, denn rein optisch verfügt man damit über eine theoretische Integer-Leistung von 2 Ops pro Takt und Kern – während K7, K8, K10, Core 2 und Nehalem für 3 Ops pro Takt und Kern stehen. Natürlich spielen bei Prozessoren die theoretischen Leistungswerte eine eher untergeordnete Rolle und es kommt viel mehr darauf an, diese Leistung auch auszunutzen – aber ein gutes Vorzeichen ist dies nicht gerade.

Es bleibt damit weiterhin das Problem, wie AMD mit diesem Nachteil auf die benötigte Grundperformance kommen will, die für ein Duell auf Augenhöhe mit Intel einfach notwendig ist und die den aktuellen AMD-Prozessoren sicherlich fehlt. Schließlich haben die aktuellen Phenom II Prozessoren gerade einmal die Pro/MHz-Leistung der Core 2 Duo/Quad Prozessoren erreicht, zu den schnelleren Nehalem-Modellen fehlen nochmals 20 bis 30 Prozent bei der Pro/MHz-Leistung. Wie man dies egalisieren will, wenn die Bulldozer-Rechenkerne gleich mal mit der Bürde einer nur 80prozentigen Pro/MHz-Leistung gegenüber einem "normalen" Rechenkern und gesenkter Anzahl der Integer-Einheiten antreten, wird die große spannende Frage bei Bulldozer.

Dabei gilt immer noch die AMD-Aussage, daß ein 16-Kern-Bulldozer im Serverbereich auf 50 Prozent mehr Performance gegenüber einem aktuellen Opteron-Prozessor von AMD mit 12 Rechenkernen kommen soll – wobei solche Vergleiche üblicherweise auf der maximalen jeweils verfügbaren Taktfrequenz und damit eben auch unter Einfluß der Taktraten gemacht werden. Abzüglich der höheren Kernanzahl muß ein Bulldozer-Kern somit entweder per Takt oder per höherer Pro/MHz-Leistung um die 12,5 Prozent (theoretisch) bis 25 Prozent (praxisnäher) mehr leisten als ein K10-basierter Opteron. Angesichts des Nachteils der Modul-Bauweise erscheint dies als hohe Aufgabe: Bei dem 80%-Penalty der Modul-Bauweise bräuchte man – mal nur die Taktrate betrachtend – satte 60 Prozent Mehrtakt, um auf die vorhergesagte Performance zu kommen.

Und dabei wären die 12,5 bis 25 Prozent höhere Pro/MHz-Leistung schließlich etwas mager, angesichts dessen was Intel zu bieten hat und mit einem kleinen Druck auf die Taktraten-Taste zusätzlich noch hervorzaubern könnte. Auch wenn die Modul-Bauweise von Bulldozer technologisch fortschrittlich ist, bleibt also weiterhin offen, wie AMD mit diesem Design die notwendige Pro/MHz-Leistung auf die Beine stellen will, um Intel im HighEnd-Bereich ernsthaft unter Druck setzen zu können. Allein mit höheren Taktraten wird man dies voraussichtlich kaum ausgleichen können – AMD wird uns mit irgendetwas überraschen müssen, um das angepeilte Performanceziel zu erreichen und nach Möglichkeit noch zu überbieten.

Davon abgesehen wäre noch zu erwähnen, daß Bulldozer SSE 4.1, SSE 4.2 und auch das neue AVX unterstützen wird – und damit alles, was auch Sandy Bridge an CPU-Befehlssatzerweiterungen anbringen wird. Die Hardware-Unterstützung für AES-NI zur schnelleren Bewältigung der AES-Verschlüsselung wurde hingegen früher schon bestätigt. Der TurboCore-Modus soll zudem generell überarbeitet werden – dies erscheint auch notwendig angesichts der teilweise erheblichen Ausweitung des TurboMode-Taktspielraums bei Sandy Bridge.

Die Bulldozer-Prozessoren des Desktop-Bereichs kommen im neuen Sockel AM3+, welcher allerdings nur eingeschränkt abwärtskompatibel ist. Zwar kann der Sockel AM3+ auch Prozessoren des Sockels AM3 aufnehmen, umgedreht können Mainboards mit dem Sockel AM3 jedoch keine Prozessoren des Sockels AM3+ aufnehmen – Bulldozer erfordert also in jedem Fall neue Mainboards. Ob diese neue Chipsätze tragen werden oder nicht, ist derzeit noch nicht sicher, ist aber angesichts des Zwangs zu neuen Mainboards sowieso zweitrangig. Damit wird man für die neuen HighEnd-Architekturen des Jahres 2011 bei AMD und Intel beiderseits nicht um ein komplett neues Grundsystem aus Mainboard und CPU herumkommen.

Nachtrag vom 26. August 2010

Wir müssen noch einmal auf das Thema der voraussichtlichen Performance von Bulldozer angesichts der neuen Informationen über den Aufbau dieser CPU-Architektur zurückkommen: AMDs Ansatz bei Bulldozer ist schließlich, die Performance von nahezu zwei Kernen mit möglichst geringem Silizium-Aufwand und auch nicht gerade der doppelten Verlustleistung hinzubekommen. Hinzu kommt noch der Punkt, daß ein Integer-Rechenkern von Bulldozer auf dem Papier nicht mehr so mächtig ist (zwei Ops pro Takt und Kern) wie die Integer-Kerne von K7, K8 und K10 oder die von Core 2 bzw. Nehalem (jeweils drei Ops pro Takt und Kern). Daß Teile der Pipeline nun zwei Integer-Kernen dienen müssen, dürfte zwar die Auslastung der Pipeline-Bausteine erhöhen, aber auch nicht unbedingt der Performance pro Rechenkern zuträglich sein.

So steht es wie gesagt auf dem Papier, allerdings gibt es gegenüber der These, daß Bulldozer damit eine niedrige Performance pro Rechenkern haben wird, gewichtige Einwände: Erstens einmal steht dem entgegen, daß die drei Integer-Einheiten der anderen genannten Prozessoren gewöhnlich sehr schlecht auszulasten sind – was auch illustriert wird durch den Punkt, daß in der Praxis die real erreichte Rechenleistung früherer Prozessoren irgendwo bei einem Ops pro Takt und Kern liegt. Der Verzicht auf die dritte Integer-Recheneinheit muß also nichts bedeuten, von der Performance pro Kern und Takt her kann Bulldozer problemlos auf der Höhe des K10-Prozessors und eventuell sogar über diesem liegen. Und zweitens bezieht sich die AMD-Aussage von der 80prozentigen Performance eines Bulldozer-Kerns gegenüber einem "regulär" aufgebauten Kern (mit denselben Einheiten, aber ohne gesharter Pipeline) explizit auf Multithread-Anwendungen.

Damit ist nicht gesagt, wie das ganze unter Singlethread-Anwendungen ausschaut – welche regulär gesehen weniger Probleme mit den gesharten Teilen der Pipeline haben sollten, weil bei Singlethread-Anwendungen schließlich der zweite Kern gar nicht (oder nur geringfügig für System-Threads) benötigt wird und alle gesharten Pipeline-Teile somit nur einem Kern zur Verfügung stehen. Beides zusammengefaßt ergibt: Derzeit läßt sich noch gar keine vernünftige Aussage zur Performance pro Kern und Takt treffen – selbst die momentan bekannten technischen Details reichen dafür nicht aus. Zudem hat das Bulldozer-Design gemäß verschiedenen Quellen das Potential zu hohen Taktraten und desweiteren gibt es noch den verbesserten TurboCore, womit sich also auch eine nicht so hohe Performance pro Kern und Takt ausgleichen lassen würde. Für den Augenblick muß einfach noch offenbleiben, wie hoch AMD mit Bulldozer hinauskommt.

Nachtrag vom 29. August 2010

Zum Bulldozer-Prozessor wurde noch eine Spezifikations-Tabelle speziell mit den Cache-Größen und -Anbindungen gefordert, anbei ist nun diese Tabelle. Sie ist leider nicht ganz vollständig, weil zu Bulldozer in diesen Fragen derzeit noch zu wenig Material vorliegt – aber allgemein gilt ja sowieso für Prozessoren, daß sich diese schwer anhand reiner Spezifikationstabellen einschätzen lassen. Gerade die Anzahl von Recheneinheiten ist bei CPUs um mehrere Faktoren unwichtiger als bei GPUs, welche sich im Gegensatz zu CPUs doch recht gut aufgrund ihrer Rohdaten einordnen lassen. Auf CPUs trifft dies wie gesagt nicht zu, womit auch die geringer gewordenen Anzahl an ALU-Einheiten in einem Bulldozer-Kern letztlich nichts sagen muß – wie an dieser Stelle schon einmal ausgeführt.

| (alles pro Kern) | K10 | Bulldozer | Core 2 | Nehalem |

|---|---|---|---|---|

| Pipeline | 12 Stufen | ? | 14 Stufen | 16 Stufen |

| Dekoder | bis zu 3 Ops | ? | bis zu 5 Ops | bis zu 5 Ops |

| Integer | 3x ALU, 2x L/S | 2x ALU, 3x L/S | 3x ALU, 2x L/S | 3x ALU, 2x L/S |

| SIMD | 2+1 (ADD, MUL, MISC), max. 128 Bit Befehlsbreite | für zwei Kerne: 2xFMA, 2xINT, max. 256 Bit Befehlsbreite | 2 (ADD, MUL), max. 128 Bit Befehlsbreite | 2+1 (ADD, MUL, Shuffle), max. 128 Bit Befehlsbreite |

| L1 Instr.-Cache | 64 kB, 2fach assoziativ, 256 Bit Bandbreite | für zwei Kerne: 64 kB, 2fach assoziativ | 32 kB, 8fach assoziativ, 128 Bit Bandbreite | 32 kB, 8fach assoziativ, 128 Bit Bandbreite |

| L1 Daten-Cache | 64 kB, 2fach assoziativ, 256 Bit Bandbreite | 16 kB | 32 kB, 8fach assoziativ, 256 Bit Bandbreite | 32 kB, 8fach assoziativ, 256 Bit Bandbreite |

| L2-Cache | 512 kB, 16fach assoziativ, 256 Bit Bandbreite | für zwei Kerne: 2 MB, 16fach assoziativ | für zwei Kerne: 6 MB, 24fach assoziativ, 256 Bit Bandbreite | 256 kB, 8fach assoziativ, 256 Bit Bandbreite |

| L3-Cache | für vier Kerne: 6 MB, 48fach assoziativ | ? | keiner | für vier Kerne: 8 MB, 16fach assoziativ |