Hauptlinks

Suchen

News des 11. April 2011

Gemäß Fudzilla soll die zum Jahreswechsel seitens AMD anstehende 28nm Southern-Islands-Generation "nur" ein Die-Shrink mit mehr Shader-Einheiten sein, aber eben ohne echte Architektur-Veränderungen. Dies wäre ein wenig enttäuschend, allerdings auch nicht ganz unlogisch, denn eigentlich wollte AMD mit der ursprünglich geplanten 32nm-Generation gewisse Architektur-Veränderungen wie die Verbreitung der Raster-Engine sowie den Umstieg zu 4-D VLIW Shader-Einheiten vornehmen. Wie bekannt konnte der 32nm-Prozeß nicht realisiert werden, womit AMD diese Generation aufteilte: Northern Islands in 40nm brachte schon den größten Teil der Architektur-Verbesserungen mit sich, aber nicht den großen Schritt bezüglich mehr Shader-Einheiten – dies wird dann Southern Islands in 28nm vorbehalten bleiben.

Allerdings gilt die Aussage von den wenigen Architektur-Veränderungen bei Southern Islands sicherlich nur für den entsprechenden HighEnd-Chip und weniger für die restlichen Chips des Southern-Islands-Portfolios. Wie bekannt hat AMD seine geplanten Architektur-Veränderungen bei Northern Islands nur bei den größeren Chips durchgezogen, die kleineren Chips sind dagegen gegenüber der vorhergehenden Evergreen-Generation (bis auf die Anzahl der Shader-Einheiten) fast unverändert. Hier kann man sicherlich vermuten, daß AMD zumindest das Konzept mit den 4-D VLIW Shader-Einheiten innerhalb der Southern-Islands-Generation auf alle Grafikchips anwenden wird – vielleicht dann auch mit einem etwas besserem Erfolg als beim RV970/Cayman-Chip aufgrund der mit diesem Chip gesammelten Erfahrungen zu diesem neuen Ansatz.

Wieviele Shader-Einheiten AMD letztlich den einzelnen Southern-Islands-Chips mitgibt, ist aber derzeit Spekulation – nicht ganz, denn über eine AMD-eigene Leistungseinordnung der Mobile-Ausführung von Southern Islands ist eine grobe Richtung für die kleineren Chips schon vorgegeben. Allerdings sind diese Daten alles andere als eindeutig – so sieht es beispielsweise nach gleich vier Grafikchips unterhalb des (im Mobile-Segment nicht vertretenen) HighEnd-Chips aus, was für AMD ungewöhnlich wäre. Man scheint hierbei gleich zwei Grafikchips für das Mainstream-Segment aufzulegen – womit die bei AMD derzeit doch recht große Lücke zwischen Performance- und Mainstream-Segment besser gefüllt werden könnte. Trotzdem ist nachfolgendes natürlich als reine Spekulation zu betrachten – wir haben halt die zur Verfügung stehenden Angaben hochgerechnet und die dabei entstehenden Lücken per Annahme gefüllt:

| Evergreen | Northern Islands | Southern Islands (Spekulation) |

|

|---|---|---|---|

| HighEnd | RV870/Cypress 1 Raster Engine (mit verdoppeltem Raster-Setup), 1600 VLIW5 Shader-Einheiten (20 SC), 80 TMUs, 32 ROPs, 256 Bit DDR Interface (bis GDDR5) |

RV970/Cayman 2 Raster Engines, 1536 VLIW4 Shader-Einheiten (24 SC), 96 TMUs, 32 ROPs, 256 Bit DDR Interface (bis GDDR5) |

"RV1090" angenommen 2560 VLIW4 Shader-Einheiten (40 SC), 160 TMUs, 48 ROPs, 384 Bit DDR Interface (bis GDDR5) |

| Performance | - | RV940/Barts 1 Raster Engine (mit verdoppeltem Raster-Setup), 1120 VLIW5 Shader-Einheiten (14 SC), 56 TMUs, 32 ROPs, 256 Bit DDR Interface (bis GDDR5) |

"RV1070" angenommen 1408 VLIW4 Shader-Einheiten (22 SC), 88 TMUs, 32 ROPs, 256 Bit DDR Interface (bis GDDR5) |

| Mainstream I | RV840/Juniper 1 Raster Engine, 800 VLIW5 Shader-Einheiten (10 SC), 40 TMUs, 16 ROPs, 128 Bit DDR Interface (bis GDDR5) |

- | "RV1040" angenommen 896 VLIW4 Shader-Einheiten (14 SC), 56 TMUs, 24 ROPs, 192 Bit DDR Interface (bis GDDR5) |

| Mainstream II | RV830/Redwood 1 Raster Engine, 400 VLIW5 Shader-Einheiten (5 SC), 20 TMUs, 8 ROPs, 128 Bit DDR Interface (bis GDDR5) |

RV930/Turks 1 Raster Engine, 480 VLIW5 Shader-Einheiten (6 SC), 24 TMUs, 16 ROPs, 128 Bit DDR Interface (bis GDDR5) |

"RV1030" angenommen 640 VLIW4 Shader-Einheiten (10 SC), 40 TMUs, 16 ROPs, 128 Bit DDR Interface (bis GDDR5) |

| LowCost | RV810/Cedar 1 Raster Engine, 80 VLIW5 Shader-Einheiten (1 SC), 8 TMUs, 4 ROPs, 64 Bit DDR Interface (bis DDR3) |

RV910/Caicos 1 Raster Engine, 160 VLIW5 Shader-Einheiten (2 SC), 8 TMUs, 4 ROPs, 64 Bit DDR Interface (bis GDDR5) |

"RV1010" angenommen 256 VLIW4 Shader-Einheiten (4 SC), 16 TMUs, 8 ROPs, 128 Bit DDR Interface (bis GDDR5) |

| Fertigung | 40nm TSMC | 40nm TSMC | 28nm TSMC |

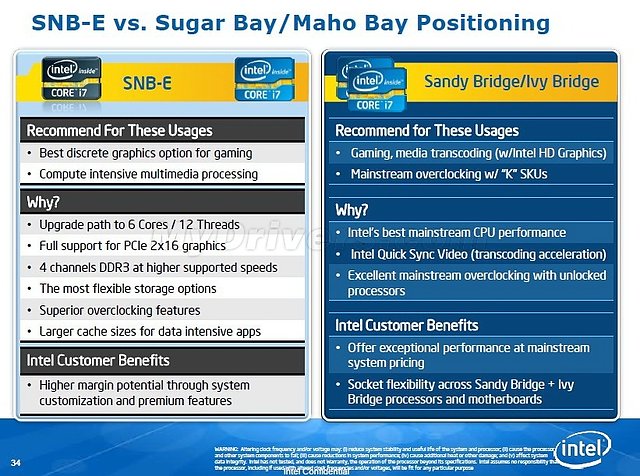

Als Nachtrag zu der am letzten Freitag gezeigten Intel-Roadmap 2011/2012 wäre noch zu erwähnen, daß die letzte (bekannte) Folie dieser Roadmap aussagt, daß es Sandy Bridge E zumindest anfänglich nur als Sechskerner (zuzüglich HyperThreading) geben wird – obwohl der benutzte Chip aus dem Workstation/Server-Segment physikalisch sicherlich ein Achtkerner sein dürfte und Intel für diesen Anwendungszweck sowieso kaum extra Sechskerner auflegen wird (die Stückzahlen sind in diesem Marktsegment zu gering für eine wirtschaftliche Fertigung). Ob sich dies halten läßt, wäre allerdings zu bezweifeln – als Sechskerner dürfte Sandy Bridge E keine große Chance gegenüber Ivy-Bridge-Vierkernern und deren Mehrtakt haben, welche bekannterweise schon ein Quartal später erscheinen werden. Vermutlich dürften spätestens im Jahr 2012 dann auch Achtkern-Prozessoren der Sandy-Bridge-E-Architektur erscheinen, um sich wieder deutlich von Ivy Bridge abzuheben – und technisch ist dies wie gesagt problemlos machbar, da die Chips physikalisch schon Achtkerner sind.

Translate

3DCenter unterstützen

Neueste Blogeinträge

Neue Forenbeiträge

- [Sammelthread] Huawei & Honor Smartphones Erfahrungen, Hardware, Software, Updates

- NVIDIA GeForce Game Ready-Treiber 595.79

- Samsung Galaxy S23 - Hyperlapse/Zeitraffer - 300x-Nachtmodus mit Ultra-Weitwinkel?

- Win 11 - Outlook 2024 und Thunderbird - keinen Zugriff, auf keinem Rechner

- Kopfhörer - Klinkenadapter für Headset an TV