Hauptlinks

Suche

AMD-Folien zu "Hawaii" zeigen Spezifikationsvergleich und Blockdiagramm

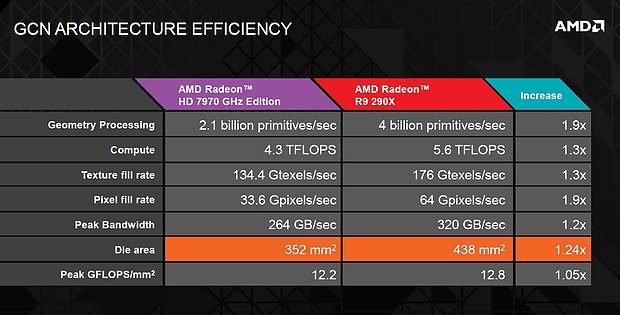

In unserem Forum sind weitere AMD-Folien zum kommenden Launch des Hawaii-Grafikchips (am Dienstag, den 15. Oktober, um 6:01 Uhr MEZ) aufgetaucht: Eine zeigt einen Vergleich der Rohleistungen von Hawaii zu R1000/Tahiti anhand der jeweiligen Spitzenmodelle Radeon R9 290X gegen Radeon HD 7970 "GHz Edition" – wobei indirekt alle schon getroffenen Feststellungen zu den Spezifikationen der Radeon R9 290X nochmals bestätigt werden (allerdings hat AMD in der jüngsten Folie die Speicherbandbreite der Radeon HD 7970 "GHz Edition" falsch angegeben, korrekt sind 288 GB/sec). Interessant ist die AMD-Angabe über die Chipfläche des R1000/Tahiti-Chips, welche erstmals mit nur 352mm² angegeben wurde – frühere AMD-Angaben beliefen sich dagegen durchgehend auf 365mm². Die Chipfläche des Hawaii-Chip wird hingegen mit 438mm² bestätigt.

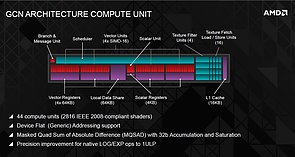

Eine andere AMD-Folie zeigt dann das Block-Diagramm des Hawaii-Chips: So sehen sind die 4 Raster-Engines ("Geometry Processor" & "Rasterizer"), welche jeweils einen Block an 11 Shader-Clustern ("CU") bedienen. Der Hawaii-Chip kommt somit auf 44 Shader-Cluster, welche jeweils 64 Shader-Einheiten tragen, was insgesamt 2816 Shader-Einheiten ergibt. Hinter dem Level2-Cache (welcher gemäß weiteren Folien allerdings nur 1 MB groß ist) sind dann die 8 64-bittigen Speichercontroller zu sehen, welche das insgesamt 512 Bit DDR große Speicherinterface des Hawaii-Chips ergeben:

AMD "Hawaii" GCN Architecture Compute Unit |

AMD "Hawaii" Render Back Ends |

AMD "Hawaii" Memory Interface |

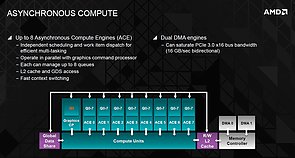

AMD "Hawaii" Asynchronous Compute |

Die Folie zum Speicherinterface zeigt im übrigen an, weshalb AMD beim Hawaii-Chip auf ein mit 512 Bit so großes Speicherinterface zu einem so durchschnittlichen Speichertakt von 2500 MHz setzte: Das größere Hawaii-Speicherinterface belegt aufgrund des niedrigen Speichertakts sogar 20% weniger Chipfläche als das "nur" 384 Bit DDR breite Speicherinterface des R1000/Tahiti-Chips.

Verwandte News

- Erste Straßenpreise zu den neuen AMD-Grafikkarten

- Erste Händler-Listungen der Radeon R9 290X sprechen für einen Listenpreis von 599 Dollar

- Übersichtsliste: Welche Hardware unterstützt welches Level von DirectX 11.x

- Nur Radeon HD 7790 & R7 260X unterstützten DirectX 11.2 vollständig in Hardware

- Stromverbrauchswerte zu Radeon R7 260X, R9 270X & 280X

- AMD gibt Euro-Preise für Radeon R7 260X, R9 270X & 280X bekannt

- Neuer Artikel: Launch-Analyse: AMD Radeon R7 240, 250 & 260X, R9 270X & 280X

- Offizielle Spezifikationen zu Radeon R9 290 & 290X aufgetaucht

- Die Grafikkarten-Performance unter der Battlefield 4 Beta

- AMD bringt Radeon R7 240, 250, 260X & R9 270X, 280X allesamt am 8. Oktober