Hauptlinks

Suche

Hardware- und Nachrichten-Links des 16./17. November 2019

Nachdem SemiAccurate vieldeutig über den Tape-Out eines neuen HighEnd-Grafikchips schreiben, welcher dann im ersten Halbjahr 2020 spruchreif werden soll, rätselt unser Forum, was damit nun gemeint sein könnte. Die erste Idee hierzu lautet "Navi 21" als dem Startschuß von AMDs Navi-2X-Serie bzw. der RDNA2-Architektur mit Hardware-RayTracing – aber dies muß offen bleiben, genauso wenig wie sicher ist, ob es sich hierbei überhaupt um einen AMD-Grafikchip handelt (die von SemiAccurate zur Meldung gesetzte Tags werden offensichtlich bewußt verschleiernd und damit falsch gesetzt). Da nicht klar ist, wann der genaue Zeitpunkt des Tape-Outs war (und solche Meldungen auch oftmals erst Wochen/Monate später nach draußen dringen), ist prinzipiell auch der GA100-Chip von nVidia zu erwähnen – der seinen Tape-Out sicherlich schon gehabt haben muß, sofern nVidia jenen neuen HPC-Chip wirklich im ersten Halbjahr 2020 vorstellen will. Insofern AMD wirklich eine breitere Serie an Navi-2X-Chips und nVidia die Ampere-Generation im Zeitrahmen Sommer bis Ende 2020 bringen wollen, ist jetzt in jedem Fall der Zeitraum, wo solcherart Tape-Out stattfinden sollten. Terminlich sollte man sich im übrigen besser nicht an jene Aussagen klammern, die das erste Halbjahr nennen – alle realistischen Anzeichen sprechen eher dafür, das bis dahin maximal erste Produktankündigungen stattfinden werden, das komplette Produkt-Portfolio dann jedoch eher erst im zweiten Halbjahr 2020 ausgerollt werden wird.

|

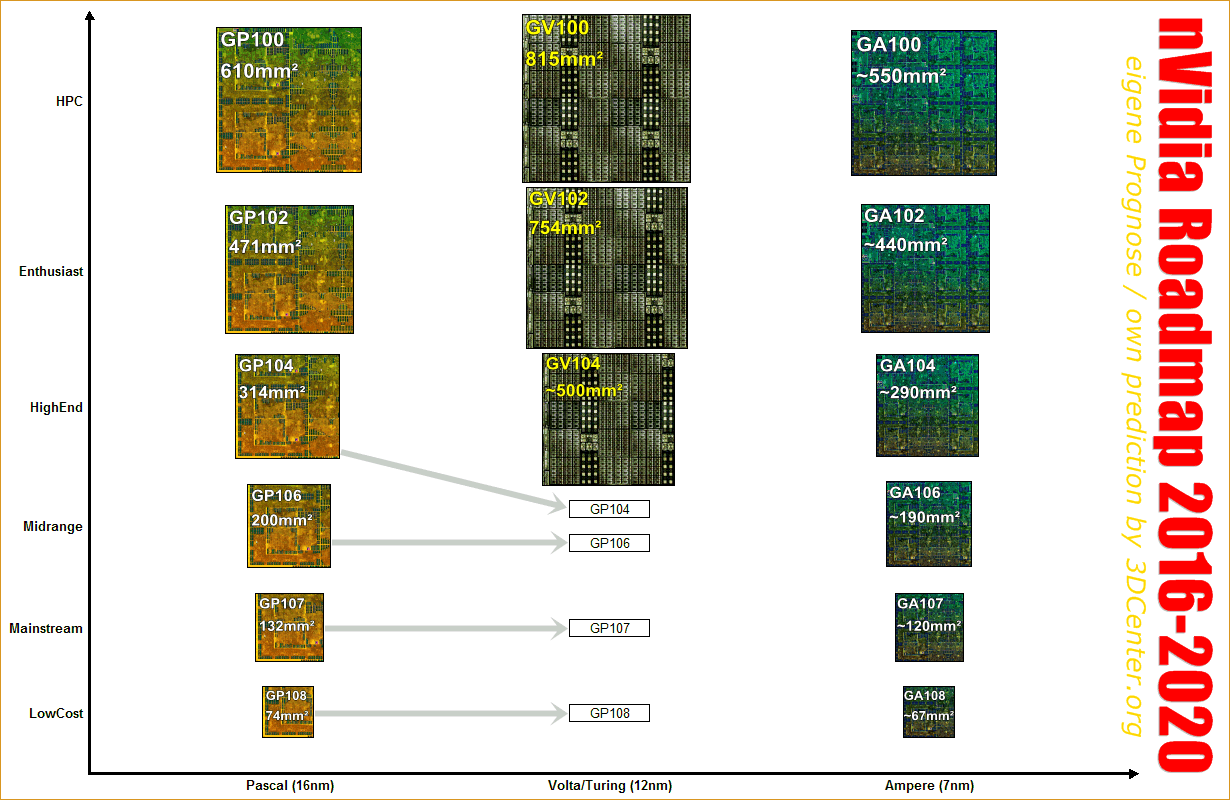

Beim Streifzug durch die Archive fiel zudem eine ältere Roadmap-Prognose auf, welche sich in den Anfangstagen der Turing-Generation auch schon der nachfolgenden Ampere-Generation widmete. Gänzlich unaktuell ist das ganze nicht, seinerzeit ging man allerdings von einer "kleinen" Turing-Generation mit nur zwei Spitzen-Chips aus, was sich wie bekannt nicht bestätigt hat. Aber ausgehend von den wirklich "fetten" Volta/Turing-Chips erwartet man seinerzeit vor allem die nachfolgende Ampere-Generation unter Ausnutzung der 7nm-Fertigung dann wieder mit kleineren Chip-Größen, ähnlich der Pascal-Generation in der 16nm-Fertigung bzw. tendentiell sogar etwas darunter. Ob nVidia diese Flächenreduktion dann allerdings bei der realen Ampere-Generation erreichen kann, ist nach den jüngsten technischen Daten zu Ampere ziemlich in Frage zu stellen: Zwischen 30% bis 70% mehr Shader-Einheiten (beim HPC-Spitzenchip augenscheinlich +50%) zuzüglich der Verdopplung der Tensor-Cores pro Shader-Cluster und anzunehmenderweise auch der Verdopplung der RT-Cores pro Shader-Cluster werden Chipfläche fressen. Zudem hat sich die 7nm-Fertigung in Bezug auf Grafikchips auch nicht als besonders Packdichten-freundlich erwiesen, AMD hat hier zwischen Vega 10 (25,3 Mio. Transistoren pro mm² unter 16nm) und Navi 10 (41,0 Mio. Transistoren pro mm² unter 7nm) nicht einmal eine echte Verdopplung hinbekommen, obwohl zwischen 16nm und 7nm nominell noch die (im PC-Bereich ausgelassene) 10nm-Fertigung liegt.

Vielleicht bekommt nVidia dies noch etwas besser hin, aber es wird angesichts dieser Ausgangslage in jedem Fall schwierig, mit wirklich kleineren Chipflächen als bei Turing anzutreten, trotz das die 7nm-Fertigung sehr teuer sein soll (und demzufolge der wirtschaftliche Anreiz zugunsten kleinerer Chipflächen erheblich ist). Der HPC-Chip GA100 mit +50% mehr Shader-Einheiten, +200% mehr Tensor-Cores, wahrscheinlich erstmals RayTracing-Cores (im HPC-Bereich) und +50% dickerem Speicherinterface soll angeblich wiederum um die 800mm² dick ausfallen, was exakt dieselbe Größenklasse wie beim vorhergehenden GV100-Chip (815mm²) darstellt. Eventuell geht nVidia dann bei den Gaming-Chips allerdings doch den Weg (etwas) kleinerer Grafikchips, eben wegen der steigenden Kostenlage der 7nm-Fertigung. Dies würde dann natürlich bedeuten, jeweils eher am unteren Ende der Hardware-Prognose zu den einzelnen Ampere-Chips herauszukommen, sprich beispielsweise beim GA102-Chip dann eher bei 6000 Shader-Einheiten als denn bei mehr als das. Trotzdem würde dies bedeuten, das die (prognostizierten) Hopper-Chipflächen nur kleiner als bei Turing herauskommen – jedoch nicht kleiner (oder gar in der Nähe) als bei Pascal.

| Segment | Chipfläche | mögliche Grafikkarten | Technik | Vorgänger-Chip(s) | |

|---|---|---|---|---|---|

| GA100 (alt. "AM100") | HPC | ~800mm² | Tesla & Titan | 8192 SE @ 6144 Bit HBM2 | GV100: 5376 SE @ 4096 Bit HBM2 |

| GA101 (alt. "AM101") | HPC | ~450mm² | Tesla & Titan | 4096 SE @ 3072 Bit HBM2 | - |

| GA102 (alt. "AM102") | Enthusiast | 600-700mm² | GeForce RTX 3080 Ti | ca. 6000-7000 Shader-Einheiten | TU102: 4608 SE @ 384 Bit GDDR6 |

| GA104 (alt. "AM104") | HighEnd | 450-500mm² | GeForce RTX 3070 & 3080 | ca. 4000-5000 Shader-Einheiten | TU104: 3072 SE @ 256 Bit GDDR6 |

| GA106 (alt. "AM106") | Midrange | 300-350mm² | GeForce RTX 3060 | ca. 2500-3000 Shader-Einheiten | TU106: 2304 SE @ 256 Bit GDDR6 TU116: 1536 SE @ 192 Bit GDDR6 |

| GA107 (alt. "AM107") | Mainstream | 200-250mm² | GeForce RTX/GTX 3050 | ca. 1500-1800 Shader-Einheiten | TU117: 1024 SE @ 128 Bit GDDR5 |

| GA108 (alt. "AM108") | LowCost | 140-170mm² | GeForce RTX/GTX 3040 | ca. 1000 Shader-Einheiten | - |

| Die Angaben dieser Tabelle zu Ampere-Chips sind voll spekulativ. | |||||

Damit der Flächenbedarf nicht ausufert, könnte nVidia im übrigen zum ersten Mal auch HBM-Interfaces zu den Gaming-Grafikchips bringen – mit dem Enthusiasten-Chip GA102 als offensichtlichem Anwendungsfall. Dessen Chipfläche dürfte bei 6000-7000 Shader-Einheiten unter der 7nm-Fertigung bei geschätzt ca. 600-700mm² liegen, wobei noch dazu die hohe Anzahl an Shader-Einheiten sowieso etwas mehr Bandbreiten-trächtigeres als ein 384 Bit GDDR6-Interface nahelegt. Ein 512 Bit breites GDDR6-Interfaces ist wahrscheinlich außerhalb der Diskussion, da zu viel Chipfläche belegend und vor allem zu viel vom Power-Budget vereinnahmend – etwas, was man sich bei diesen Enthusiasten-Lösungen mit TDPs á 250 Watt schlecht leisten kann. Insofern wäre es sogar regelrecht clever von nVidia, hierbei auf HBM zu setzen – man kann höhere Bandbreiten zu geringerem Flächenbedarf und vor allem mit geringerem Strombedarf erzielen, womit innerhalb eines festgelegten Power-Budgets letztgenannter Punkt dann wiederum für höhere Chip-Taktraten und damit einer besseren Ausnutzung der Recheneinheiten des Grafikchips nützlich ist. Letztlich liegen hierbei die gleichen Gründen vor, weswegen nVidia auch im HPC-Bereich seit zwei Generationen bereits auf HBM-Speicher setzt – und inzwischen dürfte nVidia dann auch genügend Erfahrungswerte haben, um das ganze für eine Gamer-Grafikkarte (mit demzufolge anderem Herstellungspreis und viel höheren Stückzahlen) adaptieren zu können.