Hauptlinks

Suche

Hardware- und Nachrichten-Links des 18. März 2019

Die Keynote von nVidia-Chef Jensen Huang auf der GTC 2019 brachte leider keinerlei Erwähnung einer neuen Grafikchip-Generation, egal ob des HPC- oder des Gaming-Bereichs (Video bei Ustream, Ticker bei der PC Games Hardware). Logischerweise geht es bei nVidias eigener Haus-Messe in erster Linie um professionelle Produkte, aber in der Vergangenheit wurden hier schon bedeutsame Vorstellungen abgehalten – so 2016 die der "Pascal"-Architektur mit dem GP100-Chip sowie 2017 die der "Volta"-Architektur mit dem GV100-Chip. Das es zwei Jahre später immer noch kein Lebenszeichen von einem neuen HPC-Chip seitens nVidia gibt, ist in dem Sinne dann genauso auch eine Information: Augenscheinlich dauert es noch etwas, ehe nVidia den nächsten HPC-Chip in vermutlich der Ampere-Generation spruchreif bekommt. Dies könnte darauf hindeuten, das nVidia beim zugrundeliegenden 7nm-Prozess von TSMC auf dessen EUV-Variante "7FF+" wartet, welche erst im Jahr 2020 für PC-Chips verfügbar wird. Damit ist es dann auch fast auszuschließen, das nVidia dieses Jahr noch eine neue Gaming-Generation auflegt, auch bei dieser wird man dann vermutlich auf 7FF+ warten. Das Frühjahr 2020 ist demzufolge der anzunehmenderweise früheste Termin, zu welchem neue Gaming-Chips von nVidia aus heutiger Sicht zu erwarten sind. Ein neuer HPC-Chip könnte dagegen schon früher angekündigt werden, dürfte aber ebenfalls dann erst im Jahr 2020 verfügbar werden.

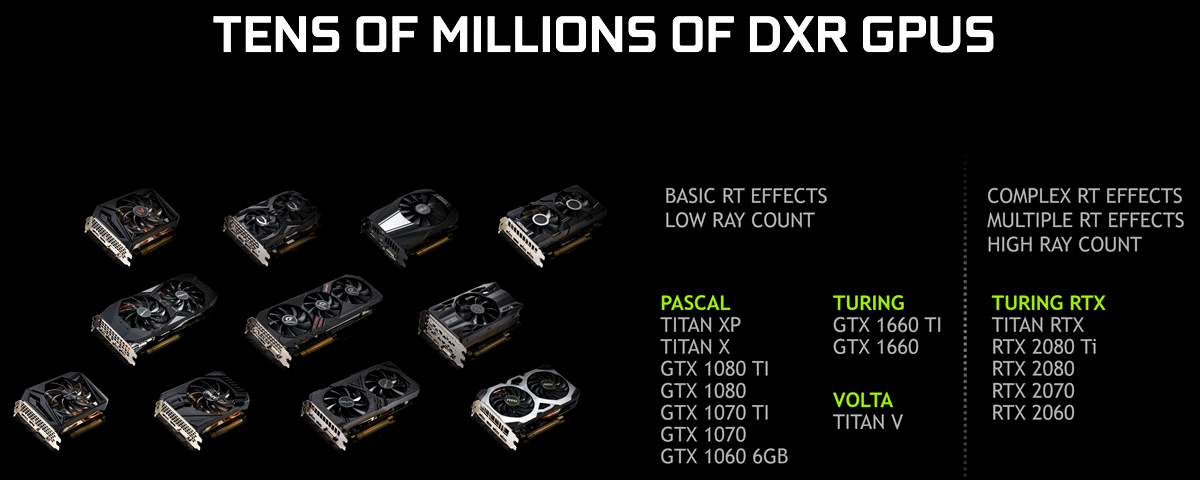

Zur zeitgleich laufenden Game Developers Conference (GDC 2019) hat nVidia einen im April zur Verfügung stehenden Grafikkarten-Treiber angekündigt, welcher RayTracing auch auf GTX-Grafikkarten ab der Pascal-Generation ermöglichen wird. Im genauen geht es ab der GeForce GTX 1060 6GB los, denn hierbei wird RayTracing – wie bei der seinerzeitigen Demonstration mit der Titan V – natürlich über die Shader-Einheiten realisiert, ist also auf LowCost- und Mainstream-Hardware aus Performance-Gründen nicht realisierbar. Gemeint ist hierbei natürlich DirectX 12 RayTracing (DXR) und damit keine Variante wie das kürzlich von Crytek vorgestellte Voxel-basierte RayTracing, welches auch ohne expliziter RayTracing-Hardware schnell genug läuft. nVidias Grafikkarten ohne RT-Cores werden DXR dann natürlich nur deutlich langsamer bzw. unter niedrigerer RayTracing-Qualität darstellen können als die RTX-Grafikkarten, nVidia spricht diesbezüglich von einem Performance-Unterschied von Faktor 2-3. Laut einer nVidia-Hochrechnung würde man daher einen (hypothetischen) Pascal-Chip mit 35 Mrd. Transistoren auf 1324mm² Chipfläche und 650 Watt Grafikkarten-Verbrauch benötigen, um unter Metro: Exodus dieselbe RayTracing-Performance wie eine GeForce RTX 2080 auf Basis des TU104-Chips mit 13,6 Mrd. Transistoren auf 545mm² Chipfläche und 215 Watt Verbrauch zu erreichen.

Mittels dieser Beispielrechnung will nVidia natürlich primär verdeutlichen, das der nVidia-Weg über die dedizierten RT-Cores sinnvoller war als einfach nur die Anzahl der Shader-Einheiten zu steigern – was wie gesagt durch die Crytek-Demonstration nunmehr etwas in Frage gestellt ist. Der kommende RayTracing-Treiber für die GTX-Grafikkarten stellt dann schlicht nur einen Software-Modus für DirectX 12 RayTracing zur Verfügung, welcher allerdings nur auf besonders leistungsstarken Grafikkarten wie der GeForce GTX 1080 Ti eine praktische Relevanz entfalten dürfte – und auf kleineren Grafikkarten dann sicherlich zu langsam ist, um praktisch überhaupt nutzfähig zu sein. Zudem könnten bzw. sollten die RayTracing-Anforderungen mit zukünftigen Spieletiteln weiter (stark) ansteigen, womit die Grenzen des RayTracings auf GTX-Grafikkarten noch schneller erreicht werden dürften. Im technologischen Weg, welchen nVidia bezüglich RayTracing gegangen ist, sind die expliziten RT-Cores und damit RTX-Grafikkarten weiterhin die Grundvoraussetzung – der RayTracing-Treiber für GTX-Grafikkarten ist dagegen grob gesehen nur für Technologie-Demos nutzvoll, nicht aber für reale Spielen.

Bei Critical Hit (via PC Games Hardware) berichtet man von einem neuen Codenamen für AMD-Prozessoren namens "Valhalla", welcher (mehrfach) in einem BIOS-Updates für ein X470-Mainboard von Biostar aufgetaucht ist. Interessanterweise scheint der Codename sich nicht auf eine einzelne CPU zu beziehen, sondern eher einen Oberbegriff darzustellen, da in selbigem BIOS-Update die bisherigen "Zen Common Options" in "Valhalla Common Options" umbenannt wurden. Dies sieht wohl ganz danach aus, als würde AMD die Zen-2-Familie nunmehr unter diesem eigenen Familien-Codenamen laufen lassen – denn die einzelnen Prozessoren dieser Generation haben allesamt schon eigene Codenamen (Desktop: Matisse, Server: Rome, HEDT: Castle Peak, APU: Renoir). Gänzlich sicher ist diese Auslegung aber noch nicht – im Fall des Falles wäre das ganze jedoch eher suboptimal, denn die Zen-2-Familie braucht eigentlich keinen extra Codenamen, "Zen 2" ist da sowohl aussagekräftig genug als auf markentechnisch (mehr als) ausreichend stark. Als Alternativthese könnte man in Betracht ziehen, das AMD den bisherigen "Matisse"-Codenamen abgeschafft und nunmehr durch "Valhalla" ersetzt haben könnte. Dies wäre dann hingegen ein sinnvoller Tausch, denn die Namen bekannter Maler als Codenamen für AMD-Prozessoren sind zumindest dann, wenn damit Performance und Leistungsstärke verdeutlicht werden sollen, eine eher suboptimale Wahl.

Aus gleichlautenden BIOS-Updates seitens Asus lassen sich hingegen diverse technische Details zu Zen 2 herauslesen – auch wenn einiges davon noch nicht gänzlich gut deutbar ist. Die Quelle hierfür liegt im Overclock.net-Forum, aber auch in unserem Forum wird über die korrekte Auslegung dieser Informationen angestrengt diskutiert. Als sicheren Punkt bestätigt das BIOS-Update erst einmal, das AMD im Desktop-Bereich (Sockel AM4) bis zu zwei Core-Chiplets ("Compute Cache Die" aka CCD) ansetzen wird – das damit erreichbare Maximum sind dann 16-Kern-Prozessoren mit 32 CPU-Threads. Ob AMD jenes Maximum vom ersten Tag an bereits in den Markt schickt, bleibt dagegen weiterhin eine offene Frage, wird mittels dieser Information nicht aufgelöst. Diskussionsstoff verbirgt sich hingegen in Punkt 6, weil jener verspricht, das jedes Core-Chiplet einen eigenen Speicherkanal (des wie üblich DualChannel-Speicherinterfaces) nutzt. Dies soll die Speicherlatenzen minimieren – wirft allerdings die Frage auf, wie man damit die maximale Speicherbandbreite erreichen kann und was passiert, wenn man auf Speicherinhalte zugreift, die mit dem jeweils anderen Speicherkanal angebunden sind.

1) New memory controller with partial error correction for nonECC memory

2) Desktop processor with two (2 CCD) chiplets on board, 32 threads maximum

3) New MBIST (Memory built-in self-test)

4) Core watchdog – is a fail/safe function used to reset a system in case the microprocessor gets lost due to address or data errors

5) XFR – at the moment I do not see anything special about it, the algorithm and limits have been updated. Scalar Controll come back with new processors.

6) Updated core control has a symmetric configuration of the active cores . In 2CCD configurations, each chiplet has its own RAM channel in order to minimize latency to memory access. 1 channel on 8 cores will be a bottleneck if you use the system in the default state.

7) PCI GEN 4 for CH7

UPD: point number 6 is questionable, perhaps there will be a special long-range interface for connecting a chiplet with IO

Quelle: Forenuser '1usmus' im Overclock.net-Forum am 17. März 2019

Im Nachtrag stellt der Poster im Overclock.net-Forum inzwischen selber in Frage, ob man diese Information derart streng auslegen sollte – eventuell verbirgt sich hier auch nur eine Nebenfunktion, welche wenig mit dem grundsätzlichen Art und Weise des Speicherzugriffs der Zen-2-Chiplets zu tun hat. Der Punkt 7 (inzwischen im Originalpost entfernt) bezieht sich im übrigen explizit auf das Asus-Mainboard "Crosshair VII Hero" (deswegen "CH7"), welches wohl trotz des zugrundeliegenden X470-Chipsatzes noch per BIOS-Update den Support für PCI Express 4.0 spendiert bekommen wird. Technisch ist dies machbar, da für PCI Express 4.0 einfach nur das Signal entsprechend solide sein muß, was auf gutklassigen bzw. modernen Platinen des Retail-Segments oftmals der Fall sein dürfte. Dann ist es eine Entscheidung der Mainboard-Hersteller, diesen Support nachträglich noch zu aktivieren. Selbiger Support gilt dann natürlich allein für die aus der CPU selber kommenden PCI Express Lanes, welche typischerweise zum Grafikkarten-Steckplatz führen. Bei den weiteren PCI Express Lanes aus dem Mainboard-Chipsatz heraus dürfte es keinen solchen nachträglichen Support von PCI Express 4.0 geben, hierfür sind dann tatsächlich ein neuer Mainboard-Chipsatz bzw. neue Mainboards erforderlich.