Hauptlinks

Suche

"Moore's Law" ist nur noch teilweise zu halten

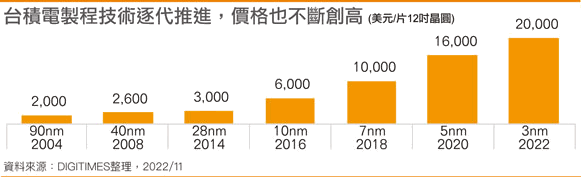

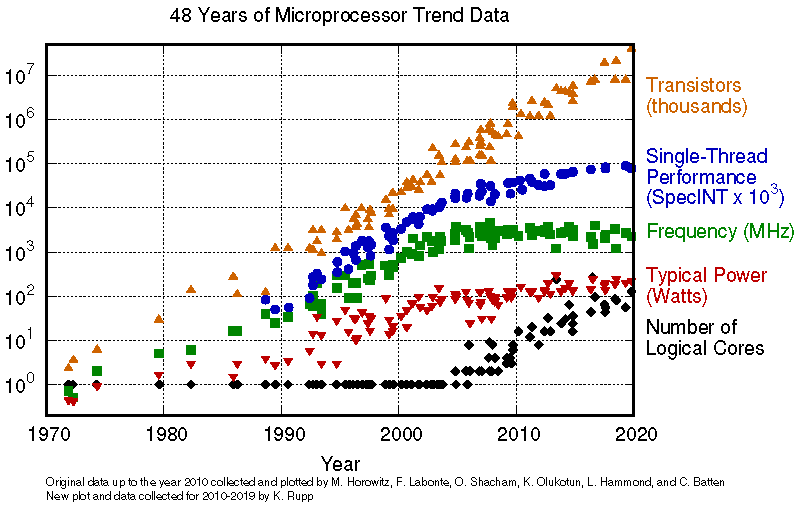

Ein von Halbleiterfertigungs-Zulieferer "Nova Ltd." kommender Artikel bei SemiAnalysis beschäftigt sich mit der Haltbarkeit von "Moore's Law" in einem sehr langfristigen Rahmen, unterteilt in grundverschiedene Phasen von dessen Wirkungsweise. Beachtenswert sind hierbei die verschiedenen Aspekte, unter welchem man jenes "Halbleiter-Gesetz" angesehen hat: Anzahl der CPU-Kerne, Stromverbrauch, Taktrate, Singlethread-Performance und Transistoren-Anzahl werden hierzu angeführt (leider nicht der Fertigungspreis). Interessant ist, dass sich "Moore's Law" bei fast allen diesen Aspekten abschwächt – nur bei der Transistoren-Anzahl nicht, jene geht auch jetzt noch steil nach oben. Aber eigentlich ist damit alles schon gesagt: Der Aufwand (und damit die Kosten) nehmen weiterhin zu, der herauskommende Effekt geht hingegen zurück. Vulgo: Man kann mehr (Transistoren) herstellen, bekommt aber nirgendwo äquivalent mehr (Performance) heraus.

48 Years of Microprocessor Trend Data — entnommen SemiAnalysis

Doch natürlich geht es für den Artikel-Schreiber aus der Fertigungs-Branche auch eher darum, immer höhere Transistoren-Mengen herauszuholen: Denn für den Chiphersteller ist die damit erreichbare Performance samt Kosten/Nutzen-Rechnung nicht so naheliegend wie für den Chipentwickler, welcher den fertigen Chip zu einem kaufbaren Gerät verarbeitet und nachfolgend im Endverbraucher-Geschäft auch wirklich absetzen muß. Damit werden in diesem Artikel auch jene zwei Punkte nicht wirklich beachtet, welche derzeit den eigentlichen Bremsklotz bilden: Erstens geht die Stromverbrauchs-Effizienz nicht mehr im gleichen Maßstab nach oben wie die Transistoren-Menge. Damit fehlt ein erhebliches Element in der Performance-Rechnung, der Performance-Gewinn pro neuer Generation kann gar nicht mehr so hoch ausfallen – oder die Verlustleistung muß dafür ansteigen, was aber in vielen Geräten nur einmal funktioniert und nirgendwo eine langfristig nutzbare Strategie darstellt.

Und zweitens limitieren die rasant steigenden Fertigungspreise pro Wafer mit jeder neuen Fertigungs-Stufe das, was die Chipentwickler letztlich an Chips tatsächlich designen. Wenn man nach einem Node-Sprung zwar doppelt so viele Transistoren zur Verfügung hat, dies jedoch mit klar höheren Preisen und steigender Verlustleistung verbunden ist, dann limitiert sich der Chipentwickler normalerweise selber: Der neue Chip kommt eben nicht mit doppelter Transistorenmenge, weil zuerst die Limits von Preis und Verlustleistung erreicht werden. Die praktisch hergestellten Chips entkoppeln sich an dieser Stelle vom reinen Fertigungsfortschritt, eben wegen der praktischen Limits von Preis und Verlustleistung. Die Generations-Fortschritte realer Produkte fallen somit (klar) geringer aus, als was der Fortschritt der Halbleiterfertigung (bei der reinen Transistoren-Menge) eigentlich ermöglichen würde.

Dies ist natürlich nur ein Teil der Ausgangslage, in der Praxis geht es auch nach Punkten, was der Markt verlangt und was der Hersteller jeweils erreichen will. Aber dies ist ein gewichtiger Teil, weil Limits nun einmal genau dies tun – sie begrenzen die Möglichkeiten: Man kann nichts zu teures für die Aufgabenstellung in den Markt drücken und dass Mittel höherer Verlustleistungen ist wie gesagt eine endliche Geschichte. Selbiges kann man 1-2mal einsetzen, nur danach befindet man sich auf einem derart hohen Verbrauchs-Sockel, dass es schon lächerlich ist und weitere Steigerungen der Verlustleistung dann auch vom Massenmarkt genauso gesehen würden. Für diesen gesamten Komplex des Fertigungsfortschritts gegenüber Kostenlage und Performance-Gewinn kann man gut AMDs neue CPUs und Grafikchips als Praxis-Beispiel ansetzen, da hier ein weitgehend klassischer Node-Sprung von 7nm auf 5nm vorliegt (im Gegensatz zu nVidias 1½-Node-Sprung und dem Fall von Intel, wo keine Angaben zu Waferkosten vorliegen).

| Zen 3 vs Zen 4 (16C) | RDNA2 vs RDNA3 (N21/N31) | |

|---|---|---|

| Fertigung | 7/12nm vs 5/6nm | 7nm vs 5/6nm |

| Transistoren | 10,5 Mrd. vs 16,4 Mrd. | 26,8 Mrd. vs 58 Mrd. |

| Chipfläche | 287mm² vs 264mm² | 520mm² vs 522mm² |

| Chipkosten (ohne Packaging) | $35 vs $60 | $104 vs $131 |

| TDP | 142W vs 230W | 300W vs 355W |

| Performance-Gewinn | +35,1% @ Anwendungen | +46,5% @ 4K (6900XT vs 7900XTX) |

| Chip-Kosten gemäß Silicon Cost Calculator, kalkuliert mit 90% Yield und folgenden (angenommenen) Wafer-Preisen: $3000 für GlobalFoundries 12nm, $10'000 für TSMC 6/7nm, $16'000 für TSMC 5nm | ||

Auf den ersten Blick spricht diese Daten-Gegenüberstellung nicht unbedingt zugunsten der vorherigen Ausführungen: Im Grafikchip-Bereich hat AMD tatsächlich die Transistoren-Menge verdoppelt, im Prozessoren-Bereich ging selbige auch ohne mehr CPU-Kerne deutlich nach oben. Aber wahrscheinlich war in beiden Fällen schon das Limit der Fertigungspreise im Blick: Jener verdoppelt sich zwischen Zen 3 und 4 nahezu – womit es für AMD kaum denkbar war, tatsächlich die doppelte Transistoren-Menge und damit einen noch größeren Leistungssprung (samt noch höherem Fertigungspreis) anzupeilen. Dagegen fällt der Kostensprung im Grafikchip-Bereich deutlich geringer aus (ca. ein Viertel mehr) – was nicht so klar zu deuten ist: Denkbarerweise hat AMD der damit erzielte Hardware-Sprung (für diese Generation) gereicht, eventuell wollte man die Kosten auch tatsächlich nicht noch höher treiben. Dass RDNA3 ein Kosten-optimiertes Design ist, sieht man jedoch spätestens an der Auslagerung der MCDs (und damit grob 2/5 der Chipfläche) zur günstigeren 6nm-Fertigung.

Selbige Problematik der Kostenoptimierung dürfte mit zukünftigen CPU- und Grafikchip-Generationen zunehmen – wo also die Chipentwickler bewußt kleinere Sprünge hinlegen, um die Kosten und Verlustleistung nicht aus dem Ruder laufen zu lassen. All dies hängt primär daran, dass "Moore's Law" nur noch in Teilaspekten die benötigte Skalierung hinlegt: Rein technologisch ist die doppelte Transistoren-Anzahl zwar weiterhin machbar, aber dafür steigt der Stromverbrauch und die Kosten – was nicht die Chipfertigung selber behindert, aber die Chipentwickler beim Design ihrer neuen Mikrochips. Jene müssen sich eben auch den Gesetzen des Marktes unterwerfen, welche bei vielen Produkten feste Power-Budgets vorgibt und oftmals nur maßvolle Preissteigerungen zuläßt. Chips könnten also in Zukunft primär aus wirtschaftlichen Gründen diese früher übliche Verdopplung durch "Moore's Law" nicht mehr mitgehen – wobei dieser wirtschaftliche Grund letztlich doch seinen Ursprung in der nicht mehr durchgehend perfekt skalierenden Fertigungstechnologie hat.

Verwandte News

- TSMCs 3nm-Fertigung wird (erneut) keine Performance-Verdopplung ermöglichen

- USA versuchen Chip-Lieferungen an Huawei per neuer Export-Beschränkungen zu unterbinden

- Simpler Grund der 14nm-Probleme: Intel muß wegen des Wettbewerbs mit AMD nunmehr viel größere Chips anbieten

- Die Flächen-normierten Fertigungskosten steigen nach dem 14/16nm-Prozeß um +30% pro Node

- Intel bringt mit der "Foveros" Technologie seinen eigenen Chiplet-Ansatz

- Der 7nm-Prozeß verdoppelt die Fertigungskosten (auf gleicher Chipfläche)

- Umfrage-Auswertung: Wann werden die ersten 7nm-basierten Gamer-Grafikkarten erwartet?

- GlobalFoundries stoppt die 7nm-Fertigung

- TSMCs 5nm-Fertigung bringt nur unterdurchschnittliche Fortschritte

- Intel bestätigt Whiskey Lake und Cascade Lake für 2018, 10nm-Produkte kommen erst im Jahr 2019