Hauptlinks

Suchen

News des 25. Juni 2010

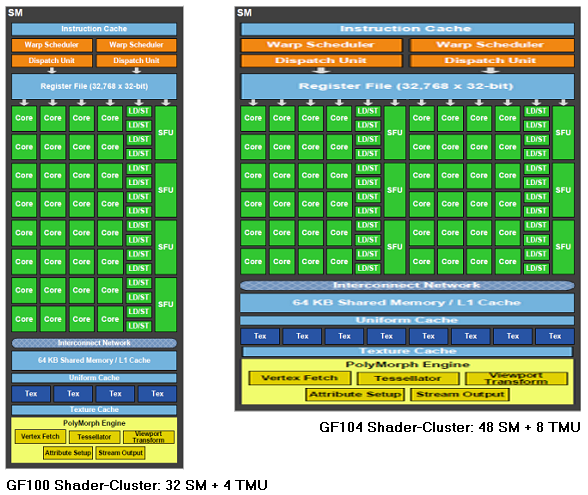

Unter tatkräftiger Mithilfe der Diskussion zu den mittwöchlichen News läßt sich in Korrektur zu diesen sagen, daß die Shader-Cluster des GF104-Chips ziemlich sicher mit 48 Shader-Einheiten (und nicht mit 24) bestückt sind, weil nur diese Zahl zu den verschiedenen kleinen Details der Fermi-Architektur passt: So muß die Anzahl der Shader-Einheiten pro Shader-Cluster immer durch 16 teilbar sein (was auf 24 nun einmal nicht zutrifft), da die Shader-Einheiten bei nVidia nicht einzelne Einheiten, sondern eigentlich Vector16-SIMD-Einheiten sind, also immer 16 Shader-Prozessoren in einer Hardware-Einheit liegen. Da zudem das Verhältnis an Shader-Einheiten zu Textureneinheiten bekannt ist (6:1 beim GF104-Chip), bleibt als einzige mögliche Auflösung nunmehr noch noch ein Modell mit 48 Shader-Einheiten (sprich drei Vec16-Einheiten) und 8 TMUs in einem Shader-Cluster.

Dieses Modell der GF104 Shader-Cluster hat dann auch andere Auswirkungen: So wird der GF104-Chip im Vollausbau nunmehr sicher 384 Shader-Einheiten und 64 TMUs besitzen, ein Modell mit 360 Shader-Einheiten ist nicht mehr möglich (weil diese Zahl nicht durch 48 teilbar ist). Für die nächstkleineren Chips GF106 und GF108 ergeben sich zudem die schon bekannten zwei Modelle: Entweder mit einer klaren Halbierung, wobei der GF106-Chip 196 Shader-Einheiten samt 32 TMUs und der GF108-Chip dann 96 Shader-Einheiten samt 16 TMUs hätte – oder aber ein Modell mit stärkerem GF106-Chip, wobei dieser auf 240 oder 288 Shader-Einheiten und der GF108-Chip dann auf 96 oder 144 Shader-Einheiten daherkommen würde. Da alle Chipgrößen (inklusive auch möglicher abgespeckter Kartenvarianten) immer durch 48 teilbar sein müssen, ergeben sich hier gar nicht all zu viele mögliche Varianten (48-96-144-192-240-288 Shader-Einheiten).

Dies setzt natürlich voraus, daß der Aufbau der Shader-Cluster bei den kleineren Chips GF106 und GF108 zum GF104-Chip identisch ist – wovon aber auszugehen ist, weil eine Neukonzeption der Shader-Cluster bei jedem einzelnen Grafikchip zu viel Entwicklungszeit und -kosten verschlingt. Der Vorteil der neuen Shader-Cluster mit den relativ vielen Shader-Einheiten würde sein, daß damit relativ gesehen weniger Einheiten verbaut würden, die direkt zum Cluster gehören – sprich, Caches, Register, Scheduler und die Polymorph-Engine. Dies spart Transistoren, was der Wirtschaftlichkeit der kleineren Grafikchips zugute kommt. Nachteiligerweise könnte damit aber auch die Tesselationsleistung wie schon angedacht bei den kleineren Grafikchips erheblich absinken: Wenn weiterhin eine Tesselationseinheit pro Shader-Cluster verbaut wird, dann hat der GF108-Chip vermutlich nur zwei Tesselationseinheiten im ganzen Chip, was gerade einmal ein Achtel der Anzahl beim GF100-Chip wäre.

| GF108 | GF106 | GF104 | GF100 | |

|---|---|---|---|---|

| Chipbasis | nVidia GF108, 40nm | nVidia GF106, 40nm | nVidia GF104, grob 2000 Millionen Transistoren in 40nm auf grob 300mm² Die-Fläche | nVidia GF100, 3000 Millionen Transistoren in 40nm auf 529mm² Die-Fläche |

| Shader-Cluster | 48 Shader-Einheiten und 8 TMUs, eine Polymorph Engine mit einer oder zwei Tesselationseinheiten | 32 Shader-Einheiten und 4 TMUs, eine Polymorph Engine mit einer Tesselationseinheit | ||

| Tesselation | 1/8 oder 1/4 GF100 | 1/4 oder 1/2 GF100 | 1/2 oder 1/1 GF100 | 100% |

| Einheiten | mehrere mögliche Varianten: 2 Shader-Cluster mit insgesamt 96 Shader-Einheiten und 16 TMUs 3 Shader-Cluster mit insgesamt 144 Shader-Einheiten und 24 TMUs |

mehrere mögliche Varianten: 4 Shader-Cluster mit insgesamt 192 Shader-Einheiten und 32 TMUs 5 Shader-Cluster mit insgesamt 240 Shader-Einheiten und 40 TMUs 6 Shader-Cluster mit insgesamt 288 Shader-Einheiten und 48 TMUs |

8 Shader-Cluster mit insgesamt 384 Shader-Einheiten und 64 TMUs | 4 Raster Engines, 16 Shader-Cluster mit insgesamt 512 Shader-Einheiten und 64 TMUs |

| Interface | 16 ROPs, 128 Bit DDR (bis GDDR5) | 24 ROPs, 192 Bit DDR (bis GDDR5) | 32 ROPs, 256 Bit DDR (bis GDDR5) | 48 ROPs, 384 Bit DDR (bis GDDR5) |

Dies wäre für die Durchsetzung von DirectX11-Tesselation eher ungünstig, weil die Spieleentwickler sich nun einmal oft nach dem kleinsten gemeinsamen Nenner richten und dieser dann die Tesselationsleistung des dutzendmillionenfach verbauten GF108-Chips wäre – welcher gerade einmal auf der (eher schwachen) Tesselationsleistung des RV870/Cypress-Chips von ATI rangieren würde. Damit steht zu befürchten, daß die hohe Tesselationsleistung der Performance- und HighEnd-Modelle von nVidias Fermi- und ATIs Southern-Islands-Generation zu Lebzeiten der entsprechenden Grafikkarten kaum in der Spielepraxis abgerufen wird. Allerdings ist dieser Punkt wie gesagt noch nicht endgültig, eventuell verbaut nVidia bei den Shader-Clustern der Grafikchips GF104, GF106 und GF108 ja auch die doppelte Anzahl an Tesselationseinheiten, dies ist derzeit schlicht noch offen. In jedem Fall fügt sich das Bild zu diesen Grafikchips nun langsam zusammen – und ab dem 12. Juli wissen wir dann (mit dem Launch der GeForce GTX 460) sowieso genau Bescheid zum GF104-Chip.

Shortcuts: Gemäß Fudzilla bringen AMDs Mainboard-Chipsätze für Fusion-Prozessoren am Jahresanfang 2011 teilweise auch den nativen Support von USB 3.0 mit sich. Damit dürfte AMD (gerade im OEM-Geschäft) einen großen Pluspunkt gegenüber Intel landen, deren nativer Support für USB 3.0 gerade erst auf das Jahr 2012 verschoben wurde. Nochmals Fudzilla berichten über Arbeiten AMDs an einer Optimus-ähnlichen Technologie, welche möglicherweise zum Endes des Jahres bereitstehen soll. nVidia hat in dieser Frage in der Tat einen gewissen Vorsprung – allerdings auch immer den Nachteil, daß man dies mit einer Intel-Plattform verbinden muß, während bei ATI/AMD alles aus einer Hand geliefert werden kann. Die X-bit Labs vermelden dagegen die Verschiebung von PCI Express 3.0 auf das Jahr 2012, nachdem die entsprechenden Komptibilitätstests erst nächstes Jahr starten werden. Damit werden die derzeit absehbaren Grafikchip-Generationen allesamt noch auf PCI Express 2.0 basieren.