Hauptlinks

Suchen

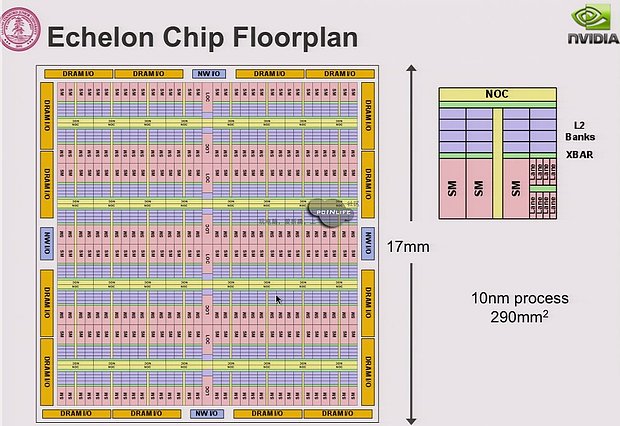

Blockdiagramme zu nVidias Echelon-Architektur für das ExaScale-Projekt

Im PCInlife Forum (wie üblich sagenhaft schwer zu erreichen) sind einige Blockdiagramme zu nVidias Echelon-Architektur für das ExaScale-Projekt aufgetaucht. Das ExaScale-Projekt bezieht sich auf eine Ausschreibung der DARPA über einen Großrechner mit einer Rechenleistung von einem ExaFlop/sec (eine Million TeraFlop/sec) für das Jahr 2018. Hierzu gehören dann nicht nur die Grafikkerne, welche die eigentliche Rechenleistung liefern sollen – sondern auch die CPUs und das Betriebssystem, faktisch also um ein komplettes System.

Demzufolge ist nVidias Echelon-Architektur für das ExaScale-Projekt höchstwahrscheinlich auch nicht mit den Consumer-Grafikchips desselben Zeitraums vergleichbar, nVidia dürfte hier etwas vollkommen eigenständiges entwickeln. Trotzdem dürften sich Anleihen der Echelon-Architektur natürlich auch in Consumer-Produkten wiederfinden – wenngleich es bis zum Jahr 2018 sowieso noch viel zu weit weg ist, um da irgendetwas seriöses prognostizieren zu können.

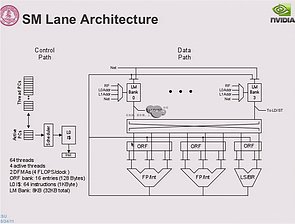

Blockdiagramm zu nVidias Echelon-Architektur (2) |

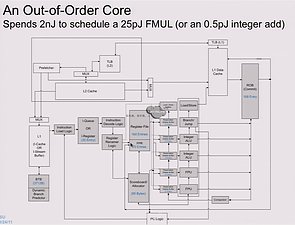

Blockdiagramm zu nVidias Echelon-Architektur (3) |

Klar ist nur, daß nVidia Echelon als 290mm² großen Chip im 10nm-Fertigungsverfahren plant. Echelon soll in dieser Ausführung über 64 "Shader Modules" (SM) verfügen, welche jeweils 32 Recheneinheiten beherbergt – dies sind vergleichsweise 2048 Shader-Einheiten. Frühere Angaben redeten allerdings von 4096 Recheneinheiten bei Echelon und dann rund 20 TeraFlop/sec pro Echelon-Chip – so oder so würde man erst in Zusammenschaltung einer sehr hohen Anzahl dieser Echelon-Chip das angepeilte Ziel von einem ExaFlop/sec erreichen. Gerade die für die Zusammenschaltung der Echelon-Chips benötigten Einheiten und Transistoren sind dann Dinge, welche eher weniger für Consumer-Produkte interessant sind. Sehr gute weiterführende Technik-Infos zu Echelon liefert zudem ein Diskussionsthread unseres Forums

Nachtrag vom 18. Januar 2012

Die Blockdiagramme stammen aus einem nVidia-Präsentation und enthalten demzufolge noch einiges mehr an Informationen. Den Link zu dieser Präsentation sowie die Diskussion dazu kann man sich in unserem Forum geben.