Hauptlinks

Suchen

Erste Details zu den Rechenkernen von AMDs Zen-Prozessorenarchitektur

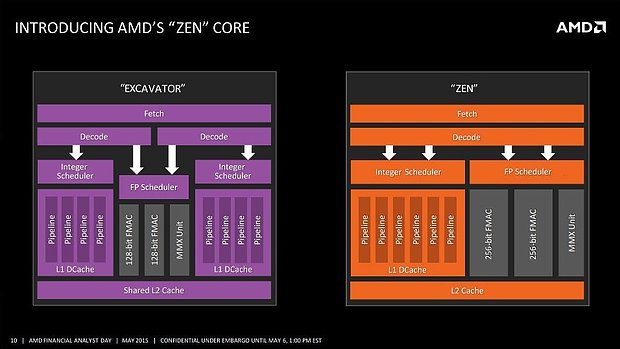

Aus dem Planet 3DNow! Forum stammen zwei Folien aus einer Präsentation, welche AMD offenbar zum kommenden "Financial Analyst Day" am 6. Mai in Bezug auf seine kommende Zen-Prozessorenarchitektur zeigen will. Die Folien zeigen zum einen den Aufbau eines einzelnen Zen-Rechenkerns im Vergleich mit dem Aufbau eines Excavator-Rechenkerns, zum anderen den Aufbau einer QuadCore-Unit aus vier Zen-Rechenkernen. Die Glaubwürdigkeit läßt sich schwer einschätzen – da zum einen so etwas unglaublich einfach zu fälschen ist (Beispiel 1 & Beispiel 2), zum anderen das Forenposting von einem regelrecht neu angemeldeten User kam. Andererseits sehen die gemachten Angaben absolut nicht unglaubwürdig oder gar übertrieben aus – sondern vielmehr eher konservativ und damit exakt so, wie das Zen-Prozessorendesign (zwischen den Zeilen) angekündigt wurde und inzwischen allgemein erwartet wird.

Der einzelne Zen-Rechenkern trägt demzufolge drei Integer-Ausführungseinheiten (sowie zusätzlich drei AGU-Einheiten), zwei 256bittige Fließkommaeinheiten (möglicherweise zusammenschaltbar zu einer einzigen 512-Bit-Einheit) samt extra MMX-Einheit. Alles hängt wieder am selben Dekoder, nur die Scheduler für Integer- und Fließkomma-Berechnungen werden getrennt. Alle errechneten Daten fließen dann in einen 512 kB großen Level2-Cache pro Rechenkern. Auch wenn nicht eingezeichnet, kommt dann wohl noch eine AMD-eigene Ausführung von SMT ("Simultaneous Multithreading", wie Intels HyperThreading) hinzu – womit ein sehr Intel-nahes Prozessorendesign herauskommen sollte, deutlich abweichend von AMDs letzten Prozessorendesigns und AMD-intern eher den K7-, K8- und K10-Prozessorendesigns nahe. Wieviel Performance dabei herauskommt, läßt sich an diesem ersten Schaubild natürlich nicht ersehen, dies kommt auf die vielen kleinen Innereien und letztlich auch auf die erreichtbare Taktrate an.

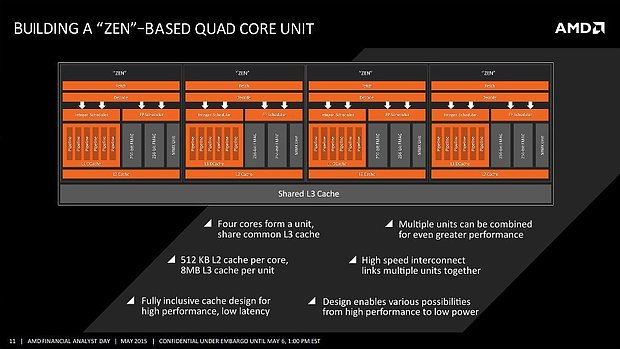

AMDs Zen-Architektur fasst dann vier dieser Zen-Rechenkerne zu einer QuadCore-Unit mit einem gemeinsamen Level3-Cache von 8 MB zusammen – welche wahrscheinlich die kleinste Grundeinheit darstellen wird, wie AMD die Zen-Rechenkerne verbaut. Wahrscheinlich werden Zen-basierte Prozessoren also nur als Vielfache dieser QuadCore-Unit erscheinen, sprich möglich sind 4, 8, 12, 16, 20, 24, usw ... Rechenkerne. Für eine Prozessoren-Architektur des Jahres 2016 (und nachfolgende) ist dies ausreichend, wahrscheinlich werden Zweikerner dann wirklich nicht mehr benötigt bzw. will AMD natürlich Intel auch wirklich angreifen und nicht nur gleichwertiges bieten. Da ein einzelner Zen-Rechenkern unter der 14nm-Fertigung nur eine Chipfläche von sogar unter 10mm² belegen soll (Haswell unter 22nm bei 14,5mm², Skylake unter 14nm dürfte ebenfalls Richtung 10mm² gehen), kann man eine solche QuadCore-Unit auf einen Flächenbedarf von ~60-70mm² schätzen. Ein kompletter Vierkern-Prozessor mit Speicherinterface und Northbridge, aber ohne integrierte Grafiklösung kommt dann auf vielleicht ~80-90mm² Chipfläche.

Damit läßt sich durchaus Staat machen, wenn man viele CPU-Rechenkerne verbauen will – anstatt viel Chipfläche für eine integrierte Grafiklösung zu opfern, so wie es Intel derzeit tut. Wenn AMD sich clever anstellt, kann man einen Achtkerner für etwas unter 200mm² Chipfläche herstellen – das wäre dann mal eine Kampfansage gegenüber Intel, deren Haswell-E Achtkerner unter der 22nm-Fertigung eine Chipfläche von 356mm² belegt, unter der 14nm-Fertigung müssten dies auch knapp 200m² ergeben. Da Intel zumindest bis inklusive der Skylake-Architektur das bekannte System – maximal Vierkerner im Consumer-Bereich, maximal Achtkerner im Bereich der E-Architekturen – beibehalten wird, ergibt sich hier für AMD durchaus die Chance, tief in diese Lücke zu stoßen und vielleicht auch mal wieder ein paar beachtbare Marktanteile zu erringen. Alles hängt natürlich daran, daß die Zen-Architektur sowohl auf echte Touren bringen kann als auch rechtzeitig in den Markt schickt, um auch wirklch noch gegen Skylake antreten zu dürfen – und nicht Intels nachfolgende 10nm-Architektur "Cannonlake" antreten zu müssen.

Verwandte News

- AMD gibt Details zur Carrizo-APU bekannt

- AMD-Prozessoren Roadmap für die Jahre 2015-2016

- Modelle und Spezifikationen zum Kaveri-Refresh "Godavari" aufgetaucht

- Neuer Artikel: Das Hardware-Jahr 2015 in der Vorschau

- Umfrage-Auswertung: Werden die Systemanforderungen für die neuen Spiele erfüllt?

- Der Windows Timer als (lösbare) Performancebremse in Spielen

- AMD kündigt Carrizo & Carrizo-L für Mitte 2015 an

- AMDs Carrizo-APU kommt mit über 3 Milliarden Transistoren

- Umfrage-Auswertung: Werden Prozessoren bewußt auf eine bestimmte TDP hin gekauft?

- Die Systemanforderungen für die PC-Spiele 2014/2015