Paralleler Bus vs. seriellem Punkt zu Punkt

Hauptlinks

Suche

Paralleler Bus vs. seriellem Punkt zu Punkt

Paralleler Bus vs. seriellem Punkt zu Punkt oder: Das Sterben der Busse

In diesem Techlet geht es um die wichtigsten Unterschiede zwischen parallelen Bussen und so genannten Point to Point, also Punkt zu Punkt Links. Warum es sie gibt, warum sie sind, wie sie sind, und warum parallele Busverbindungen immer öfter durch serielle Links ersetzt werden. Typische Vertreter für parallele Busse sind beispielsweise der PCI-Bus oder die PATA-Festplattenanschlüsse, welche nun nach und nach durch ihre seriellen Nachfolger PCI Express und SATA verdrängt werden.

Parallel: breit und stark

Dazu ist zunächst ein kleiner Ausflug in die Geschichte der Desktop-Computer und Elektronik notwendig. Bei der Festlegung der Normen für den IBM-PC und dessen Nachfolger musste man natürlich, genau wie heute, Rücksicht auf das technisch und vor allem finanziell Machbare nehmen. Es gab Schaltkreise, die preiswert ziemliche Mengen Transistoren und Logik integrierten. Problematisch waren aber hohe Frequenzen. Nicht nur für die Elektronik, sondern auch für Kabel, Leiterbahnen und Verbindungen. Also ordnete man mehrere Datenleitungen nebeneinander an und konnte so mit niedrigen Frequenzen die Daten gleich 4-Byte-weise quer durch den PC schicken.

Mit dieser Lösung handelte man sich aber auch Nachteile ein, zum Beispiel ein komplexes und platzfressendes Design. Also gibt es üblicherweise nur einen PCI-Bus, nur 2 PATA-Anschlüsse und nur einen Frontsidebus, die sich die angebundenen Geräte brüderlich teilen müssen.

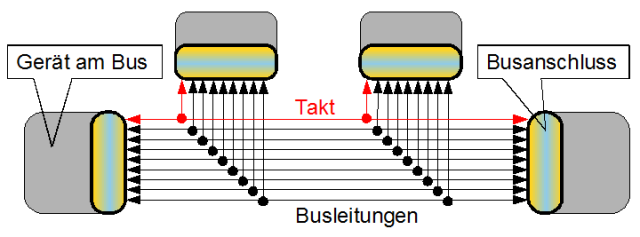

Zur Verdeutlichung hier eine Darstellung eines einfachen 8-Bit Busses plus Taktsignal (rot) ohne Interruptleitungen:

Im obigem Diagramm sind die Sendeschaltungen gelb und die Empfänger in blau dargestellt. Bei einem parallelen Busanschluss sind diese Schaltungsteile eng ineinander verflochten, was die Farbübergange veranschaulichen. Eines der Geräte am Bus ist der Buscontroller und bestimmt, wer senden darf und wer sich tot stellen muss.

Will ein Gerät auf den Bus senden, muss es entweder warten, bis es dran ist, oder per Interrupt dem Buscontroller mitteilen, dass es senden will. Dann werden die Busanschlüsse auf Senden gestellt, und die Daten werden synchron mit dem Takt per Spannungspegel auf den Bus übertragen. Die anderen Geräte müssen in dieser Zeit ihre Ausgänge komplett abschalten, und zwar aus folgendem Grund: Logisch "0" ist elektrisch Low-Pegel und das heißt bei CMOS-Schaltkreisen, dass der masseseitige Ausgangstransistor voll durchgeschaltet ist. Sendet ein anderes Gerät eine logische "1" mittels High-Pegel auf eine Busleitung, steuert hier der Ausgangstransistor zwischen Ausgang und Betriebsspannung durch.

Stehen jetzt andere Ausgänge auf Low, wird die Ausgangsspannung einfach darüber kurzgeschlossen. Es gäbe keinen sicher erkennbaren Spannungspegel und im Extremfall könnte der Ausgang sogar zerstört werden. Deshalb braucht man so genannte Tristate-Ausgänge. Neben den elektrischen Pegeln High und Low müssen diese auch auf "hochohmig" schalten können. Das heißt, dass beide Ausgangstransistoren gleichzeitig gesperrt werden müssen, um die momentan inaktiven Ausgänge sicher von der Busleitung zu trennen, der Busanschluss muss sich also wirklich regelrecht tot stellen.

Schon auf der vereinfachten Zeichnung kann man erkennen, dass da eine Menge Last an den einzelnen Leitungen hängt. Mehrere Geräte mit jeweils abgeschaltetem Ausgang und ihrem Eingang belasten den Bus, dazu kommt das Leitungsnetz auf dem Mainboard oder das Flachbandkabel bei PATA und darüber hinaus auch noch leere Slots. Alle Teile, ob in den Chips verborgen oder offen als Leitung oder Kontakt, all das sind sozusagen kleine Kondensatoren gegen Masse und gegeneinander, die auch bei jedem Pegelwechsel mit umgeladen werden müssen.

Dieser ganze Ballast verhindert erfolgreich, mal schnell eine neue Version mit höherem Takt einzuführen. PCI kam im Desktop-Bereich nie über 33 MHz hinaus, PATA mit 133 MB/s war ein Experiment, bei dem schon die meisten Festplatten-Hersteller nicht mehr mitgemacht haben. Der gute alte Parallelport muss auch noch mit langen Kabeln kämpfen, und ist daher auch nicht zu beschleunigen.

Die einzigen wirklich schnellen parallelen Busse in heutigen PCs sind der Frontsidebus und der Speicherbus. Beide schaffen nur mit hohem technischem Aufwand ihre hohen Frequenzen und Datenraten. Sie sind nur auf kurzen Strecken zuverlässig, die Ausgangsstufen müssen sich ständig an die Last anpassen, die Busse sind aufwendig terminiert und die Anzahl der Geräte am Bus ist eng begrenzt, wie z.B. beim Athlon 64 für den Sockel 939 deutlich wurde, der bei vollem Takt nur ein zweiseitiges oder zwei einseitige Speichermodule pro Kanal sicher betreiben konnte.

Ein weiteres Problem, welches die Platinendesigner betrifft, ist die Gleichzeitigkeit der Signale. Es müssen immer alle Bits gleichzeitig ankommen. Schaltet der Takt schon um, ehe alle Bits stabil anliegen, gibt es Datenfehler. Bei Takten von mehreren hundert Megahertz reichen schon einige Millimeter Längenunterschied der Leitungen, um merkliche Laufzeitdifferenzen zu erzeugen. Was also tun, wenn die Anschlüsse an den Chips nun mal nicht millimetergenau in einer Reihe stehen?

Die Lösung sieht dann so aus:

Immer komplexere Elektroniktricks sind also offensichtlich kein Allheilmittel, um mit parallelen Bussen höhere Frequenzen und Datenraten zu erreichen.