- Startseite

- News

- 7-Tage-News

- Linklisten der News

- Newsindex-Übersicht

- AMD RDNA3

- AMD RDNA4

- AMD RDNA5

- Intel Xe

- Intel Battlemage

- Intel Celestial

- nVidia Ada Lovelace

- nVidia Blackwell

- nVidia Rubin

- AMD Zen 4

- AMD Zen 5

- AMD Zen 6

- Intel Raptor Lake

- Intel Meteor Lake

- Intel Lunar Lake

- Intel Arrow Lake

- Intel Panther Lake

- Intel Nova Lake

- Artikel

- Downloads

Hauptlinks

Suchen

14Gerüchteküche: AMDs Navi 31 mit 384-Bit-Interface, 192 MB Infinity Cache und optional 192 MB 3D V-Cache

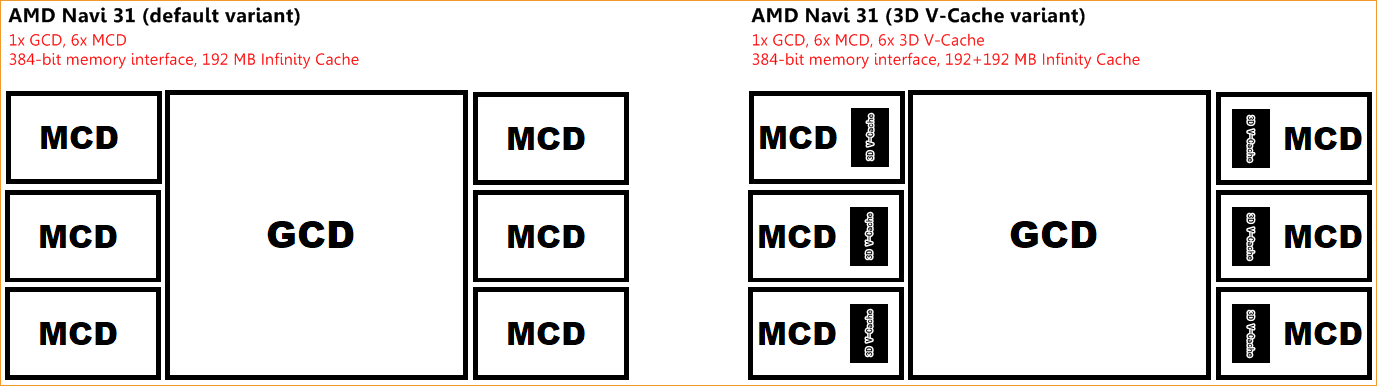

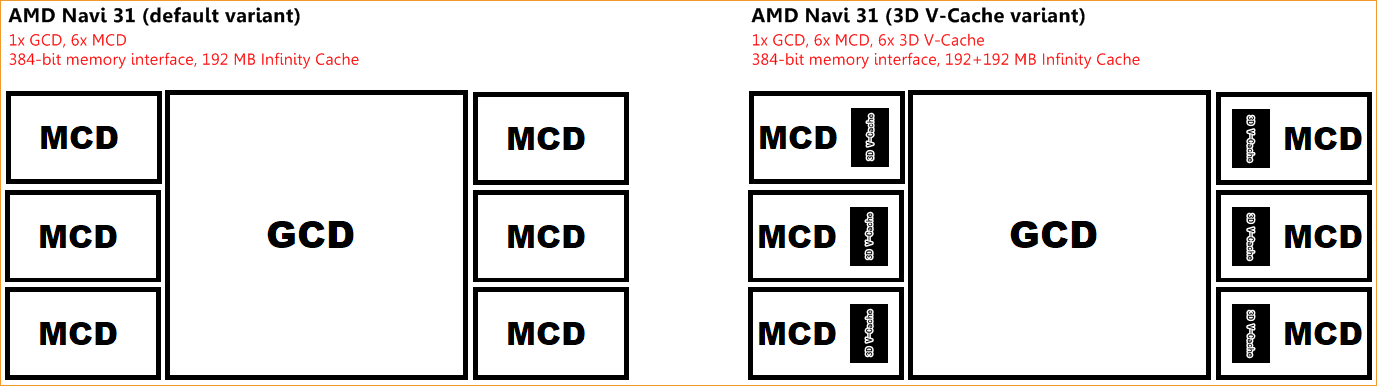

AMD Navi 31 Varianten ohne/mit extra 3D V-Cache (inoffiziell)

PS: Reines Gedankenspiel, nicht basierend auf offiziellen Daten ... Variante ohne extra 3D V-Cache entnommen von Kepler_L2

Gerüchteküche: AMDs Navi 31 mit 384-Bit-Interface, 192 MB Infinity Cache und optional 192 MB 3D V-Cache

Laut Twitterer Kepler_L2 sind für AMDs RDNA3-MCDs erste Einträge in Linux-Treibern aufgetaucht, welche gute Hinweise auf die dahinterliegende Technik liefern. So werden für Navi 31 ganze 6 dieser MCDs genannt, was wohl die Existenz eines 384-Bit-Speicherinterfaces bestätigt. Die MCDs hängen technisch in jedem Fall mit dem Speicherinterface zusammen, ein MCD steht dabei für ein 64-Bit-Teilinterface (6 x 64 Bit = 384 Bit). Bislang war allerdings unklar, ob die MCDs das Speicherinterface auch selber tragen. Die Namenswahl mit "Memory Complex Die" oder "Memory Controller Die" legt dies sicherlich nahe, allerdings konnte man sich bisher ein ausgelagertes Speicherinterface bei Grafikchips nicht so recht vorstellen. Laut Kepler_L2 soll dies allerdings tatsächlich derart passiert: Ein MCD soll ein 64-Bit-Teilinterface tragen – samt 32 MB Infinity Cache:

MCD accidentally leaked in first patch, now renamed to "UMC_Node".

(Link #1 + Link #2)

Quelle: Kepler_L2 @ Twitter am 13. Juli 2022

32MB + 64-bit MC normally, +32MB 3D V-Cache on some models.

Quelle: Kepler_L2 @ Twitter am 13. Juli 2022

Dies ist allerdings klar der Auslegungs-Teil des Ganzen – im Gegensatz zur Größe des Speicherinterface, womit frühere Gerüchte bestätigt werden. Sehr interessant ist dann auch noch der zweite Teil jener Auslegung: Denn es soll einen optionalen weiteren Infinity Cache geben, welcher in Form von "3D V-Cache" daherkommt – sprich mit draufgepappten Cache-Bausteinen, wie beim Ryzen 7 5800X3D. Damit sollen dann insgesamt 384 MB Infinity Cache bei Navi 31 möglich sein, welcher in der default-Variante allerdings nur 192 MB trägt. Hier bekommt AMD also eine gute Möglichkeit zur Produkt-Differenzierung an die Hand, gleichzeitig wird die Standard-Variante (von Navi 31) etwas billiger herzustellen sein. Wirklich bestätigt ist diese Auslegung natürlich nicht, auch in den von AMD gelieferten Linux-Patches findet sich zu den Punkten Cache-Größe und optionalem 3D V-Cache kein Hinweis.

Auf Navi 32 kann man diese Informationen derzeit leider nur interpolieren, genaueres zu diesem Grafikchip fehlt weitgehend. Aller Vermutung nach ist AMD bei Navi 32 die gleichen Schritte gegangen wie bei Navi 31: Anzahl der Shader-Cluster runter, Taktrate rauf – und dafür auch Speicherinterface hoch und Menge des Infinity Caches nach oben. Navi 32 dürfte demzufolge bei einem 256-Bit-Speicherinterface landen, mit default-mäßig 128 MB Infinity Cache und optional weiteren 128 MB Infinity Cache per 3D V-Cache. Ob dann auch Navi 33 eine Extra-Ladung "Infinity Cache" tragen kann, ist ungewiss, aber eher unwahrscheinlich: Der 3D V-Cache ist bei RDNA3 augenscheinlich zur Verwendung auf den MCDs gedacht – und könnte somit für ein rein monolithisches Design wie Navi 33 technisch bedingt nicht geeignet sein.

| Navi 33 | Navi 32 | Navi 31 | Navi 3X | |

|---|---|---|---|---|

| Chip(s) | monolithisch | vermutlich 1 GCD + 4 MCDs | 1 GCD + 6 MCDs | vermutlich 2 GCD + 8 MCDs |

| Fertigung | 6nm TSMC | GCDs: 5nm TSMC, MCDs: 6nm TSMC | ||

| Hardware-Daten | 2 Shader-Engines, 16 WGP mit 4096 FP32-Einheiten | 4 Shader-Engines, 32 WGP mit 8192 FP32-Einheiten | 6 Shader-Engines, 48 WGP mit 12'288 FP32-Einheiten | 8 Shader-Engines, 64 WGP mit 16'384 FP32-Einheiten |

| Speicherinterface | 128 Bit GDDR6 | 256 Bit GDDR6 | 384 Bit GDDR6 | 2x 256 Bit GDDR6 |

| Chiptakt | ~2.8-3.0 GHz | ? | ~3.0 GHz | ? |

| Infinity Cache | 128 MB | vermutlich 128 MB, zzgl. optional 128 MB per 3D V-Cache | angeblich 192 MB, zzgl. optional 192 MB per 3D V-Cache | vermutlich 256 MB, zzgl. optional 256 MB per 3D V-Cache |

| Speichermenge | 8/16 GB | 16 GB | 24 GB | 32 GB |

| Performance-Ziel | gegenüber 6900XT: grob gleiche Performance (FullHD etwas besser, 4K etwas schlechter) | unbekannt | gegenüber 6900XT: 2,0-2,25fache unter 4K, 2,7-3,5fache oder besser unter RayTracing | unbekannt |

| Tape-Out | Q4/2021 | Q1/2022 | Q3/2021 | kein eigener Tape-Out, da Navi-32-basierend |

| Release | unsicher | unsicher | unsicher | reines Konzept |

| Anmerkung: reine Wiedergabe des aktuellen Gerüchte-Standes – keine offiziellen Daten | ||||

Laut nochmals Kepler_L2 kann man sich ein solches Design von GCD und MCD vergleichsweise einfach aufgebaut vorstellen: Ein GCD in der Mitte, die MCDs drum herum angeordnet – fast wie das frühere Design des Fiji-Chips mit seinem HBM-Speicher Seite an Seite zum Grafikchip. Der extra 3D V-Cache dürfte dann auf die MCDs gestappelt sein – schon allein deshalb, weil dort deren Anbindung liegt (beim Ryzen 7 5800X3D wird genauso der 3D V-Cache direkt auf den Chip-Teil mit dem Level3-Cache oben drauf gepappt). Das ganze ist dann Fürwahr ein echtes Chiplet-Design, in der Spitze sollte es somit bis zu 13 Einzelchips bei Navi 31 geben. Für eine Dual-GCD-Variante von Navi 32 könnte es sogar auf bis zu 18 Einzel-Chips hinauslaufen – sofern jenes Konzept jemals realisiert wird.

AMD Navi 31 Varianten ohne/mit extra 3D V-Cache (inoffiziell)

PS: Reines Gedankenspiel, nicht basierend auf offiziellen Daten ... Variante ohne extra 3D V-Cache entnommen von Kepler_L2

Verwandte News

- Umfrage-Auswertung: Wie ist der Ersteindruck zu AMDs Radeon RX 6650 XT?

- Umfrage-Auswertung: Wie ist der Ersteindruck zu AMDs Radeon RX 6750 XT?

- AMD zeigt neue CPU/GPU-Roadmaps sowie Ausblicke auf Zen 4 & RDNA3

- Die Grafikchip- und Grafikkarten-Marktanteile im ersten Quartal 2022

- Umfrage-Auswertung: Wie ist der Ersteindruck zu AMDs Radeon RX 6950 XT?

- Neuer Artikel: Grafikkarten-Marktüberblick Mai 2022

- Umfrage-Auswertung: Wo liegt das persönliche TDP-Limit für Grafikkarten?

- Erster Test des Radeon RX 6950 XT Referenzdesigns ermöglicht Direkt-Vergleich zu den Werksübertaktungen

- Gerüchteküche: Speicherinterface von Navi 32 & Navi 31 auf 256 bzw. 384 Bit hochgestuft

- Neuer Artikel: Launch-Analyse AMD Radeon RX 6x50 Refresh