Hauptlinks

Suche

Intels "Advancing Moore's Law" Präsentation

Die Präsentation, welche Intel bei seinem kürzlichen Investoren-Meeting unter dem Titel "Advancing Moore's Law" (PDF) gezeigt hat, ist einfach zu hübsch, um jene nicht noch einmal extra zu betrachten (und damit gleichzeitig an dieser Stelle zu sichern). Primär ging es Intel bei dieser Präsentation natürlich darum, Eindruck bei den anwesenden Börsenanalysten und Investoren zu schinden – in dem man den eigenen Fortschritt in der Entwicklung neuer Fertigungstechnologien bestmöglich darstellt und die Fortschritte der Konkurrenten in Abrede zu stellen versucht. Einen gewissen Spielraum zwischen den Intel-Angaben und (realistischerweise kaum erhältlichen) unabhängigen Analysen sollte man hierbei also einkalkulieren.

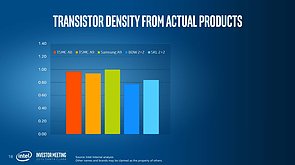

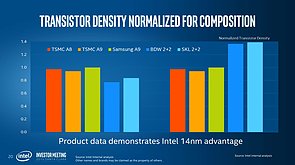

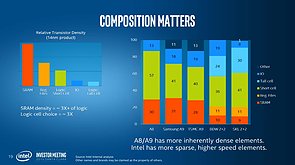

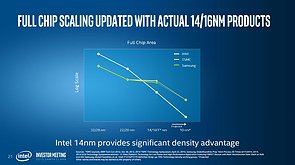

So konzentrierte sich Intel bei seinem Vergleich mit anderen Chipfertigern vor allem auf den Punkt, daß deren nominell inzwischen sogar Intel leicht überbietende hohe Transistorendichte in erster Linie aus dem Umstand resultiert, daß jene Konkurrenzprodukte aus dem Smartphone-Bereich aus wesentlich mehr "einfachen" Transistoren wie SRAM oder kleine Logikbausteine bestehen, Intels Prozessoren hingegen erheblich mehr "komplizierte" Transistoren wie große Logikbausteine beinhalten. Diese "einfachen" Transistoren lassen sich dann natürlich (sehr) viel dichter packen, womit bei einem Chip mit vielen "einfachen" Transistoren auch schnell hohe Packdichten auf den gesamten Chip gerechnet erreicht werden können.

Intel versucht dann mit seinen Ausführungen auf den Punkt hinzuweisen, daß eine einfache Transistorendichten-Rechnung nicht zielführend ist, weil jene den unterschiedlichen Chipdesigns nicht gerecht wird. Man macht hingegen eine eigene Rechnung auf Basis normalisierter Transistorengrößen auf – unter welcher Intel dann deutlich besser wegkommt als die Konkurrenz aus dem Smartphone-Lager. Ob das ganze allerdings überhaupt einen sinnvollen Vergleich darstellt, bleibt anzuzweifeln: Die Aufgabengebiete dieser Prozessoren sind zu verschieden, vor allem aber die Taktraten sind gänzlich anders: Bei Smartphones in der Spitze 2 GHz, welche aber fast nirgendwo dauerhaft zu halten sind – und bei PC-Prozessoren in der Spitze 4 GHz, welche notfalls dauerhaft zu halten sind. Hierfür sind gänzlich andere Transistoren und vor allem Packdichten als vollkommen normal anzusehen, die jeweiligen Chipsdesigns müssen halt völlig unterschiedliche Taktraten aushalten. Hier müssen sich eher die Betrachtungen der Analysten der vorhandenen technischen Realität anpassen, Intel braucht in dieser Frage keine zwangsweise Gleichwertigkeit zu simulieren.

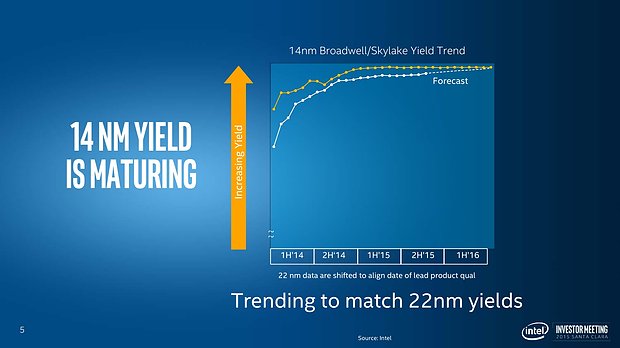

Noch viel mehr diskutabel und zudem viel interessanter sind Intels Ausführungen zu den Fortschritten bei der Produktionsausbeute der 14nm-Fertigung sowie zur Kostenprojektion für die kommenden Intel-Fertigungen. Erst einmal ist Intel bei der 14nm-Produktionsausbeute schon nahe dran an der 22nm-Produktionsausbeute – wenn Intel sagt, daß man hier erst im Sommer 2016 einen Gleichstand erreicht haben will, dann handelt es sich um einen Kampf um die letzten Prozentpunkte, jedoch mitnichten um elementare Unterschiede. Sprich: Die aktuelle Lieferschwäche von Intel gerade bei Skylake-Vierkernern kann kaum aus dieser (minimal) schlechteren Produktionsausbeute resultieren, sondern wird einen anderen Grund haben müssen. Der erste Verdacht richtet sich hierbei auf eine für den bestehenden Bedarf noch nicht ausreichende Anzahl an 14nm-Fertigungsstraßen – alternativ selektive Fertigungsprobleme nur beim Vierkern-Die oder auch eine falsche Bedarfskalkulation zwischen Zwei- und Vierkern-Dies.

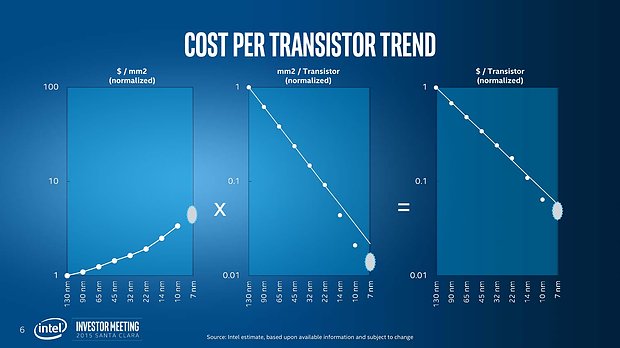

Und zweitens geht es um die Kostenprojektion für die kommenden 10nm- und 7nm-Fertigungen, zu welchen sich Intel erhebliche und sogar überdurchschnittliche Vorteile bescheinigt bzw. eher denn prophezeit. Damit will man primär Analysten-Befürchtungen entgegentreten, durch die steigenden Forschungs- und Umrüstkosten für jede neue Fertigungsstufe würde eine solche irgendwann einmal zu teuer werden, um noch Sinn zu machen. Allerdings ist es wohl so, daß jene Kostensteigerungen immer noch weit entfernt von den Vorteilen bei der Flächenreduktion sind – wo immer noch recht zuverlässig grob -50% zwischen zwei Fertigungsstufen erreicht werden. Durch die Kostensteigerung bei kommenden Fertigungsverfahren ist dann kein gleichwertiger Kostenvorteil von -50% pro Transistor mehr zu erreichen, aber der Preis pro Transistor sinkt trotzdem erheblich, wird also nicht gerade höher ausfallen als vorher. Damit ist es auch langfristig sinnvoll, faktisch alles irgendwann auf die neue Fertigung umzusetzen – natürlich erst dann, wenn dafür die entsprechenden Fertigungskapzitäten zur Verfügung stehen.

Intel sieht den Punkt der steigenden Kosten pro Transistor bei neueren Fertigungsverfahren gemäß seiner Folie allerdings anders: Man will nicht nur eine gleichwertige Kostenreduktion bei 10nm und 7nm erreichen, sondern vielmehr soll die Kostenreduktion (pro Transistor) unter diesen kommenden Fertigungsverfahren sogar besser ausfallen als bei früheren Fertigungsverfahren. Wie dies angesichts der technologischen Ausgangslage funktionieren soll, erklärt Intel den Analysten natürlich besser nicht – ansonsten könnte jenen aufgehen, daß man hierbei den Heiligen Gral der Chipfertigung verspricht: Immer höhere Zugewinne bei technisch immer schwieriger werdender Ausgangslage. Dies dürfte in dieser Form nicht passieren, auch Intel kocht bei all seinem technologischen Vorsprung nur mit Wasser.

Eher glaubwürdig sind in dieser Frage frühere Ausführungen von AMD, welche immer kleiner werdende Zugewinne und höhere Kostenlagen bei neuen Fertigungsverfahren versprechen. Jene immer kleiner werdenden Zugewinne auf technologischer Seite (Flächenvorteil, Taktratenvorteil & geringerer Stromverbrauch) kann man zwar maximieren, in dem man (wie Intel derzeit) die Zeitspanne zwischen zwei Fertigungsverfahren streckt und somit faktisch mehr Technik in eine neue Fertigung steckt als die Konkurrenz. Bei der Kostenlage ergibt sich damit jedoch kein Vorteil, sondern eine weitere Kostenzunahme – mehr Entwicklungszeit und höherwertige Technik schlagen immer zu Buche, dies würde sich nur über gravierende technologische Durchbrüche abmildern lassen, die aber auch nicht vom Himmel fallen. Egal, wie herum man es angeht: Neue Fertigungsverfahren werden teurer, es ergibt sich hierbei ein immer größerer werdender Unterschied zwischen erreichtem technologischen Vorteil (machbar) und erreichter Kostenreduktion (immer schwieriger).

| Beispielrechnung auf der Basis rein angenommener Werte | |||||

|---|---|---|---|---|---|

| 28nm | 14nm | 10mm | 7nm | 5nm | |

| angenommene Flächenreduktion | -50% | -50% | -50% | -50% | |

| Beispiel 1: angenommene Kostenreduktion pro Transistor | -50% | -50% | -50% | -50% | |

| Beispiel 1: Herstellungspreis eines angenommenen Chips mit jeweils gleicher Chipfläche | 100$ | 100$ | 100$ | 100$ | 100$ |

| Beispiel 2: angenommene Kostenreduktion pro Transistor | -45% | -45% | -45% | -45% | |

| Beispiel 2: Herstellungspreis eines angenommenen Chips mit jeweils gleicher Chipfläche | 100$ | 110$ | 121$ | 133$ | 146$ |

| Beispiel 3: angenommene Kostenreduktion pro Transistor | -40% | -35% | -35% | -30% | |

| Beispiel 3: Herstellungspreis eines angenommenen Chips mit jeweils gleicher Chipfläche | 100$ | 120$ | 156$ | 203$ | 218$ |

| Beispiel 4: angenommene Kostenreduktion pro Transistor | -35% | -30% | -25% | -20% | |

| Beispiel 4: Herstellungspreis eines angenommenen Chips mit jeweils gleicher Chipfläche | 100$ | 130$ | 182$ | 273$ | 437$ |

Die Kosten pro Transistor werden zwar weiterhin (sogar erheblich) absinken, die Kosten eines Chips mit jeweils gleicher Chipfläche (wie beispielsweise ein Enthusiasten-Grafikchip á 600mm² Chipfläche) werden allerdings durch letztgenannten Effekt steigen – und dies mit jedem kommenden neuen Fertigungsverfahren immer stärker. Über mehrere Fertigungsverfahren hinweg kann sich dabei durchaus eine Kostenverdopplung für jenen bespielhaften Grafikchip ergeben – in Folge dessen müssen die Abgabepreise hoch, oder man muß sich überlegen, ob so große Chips überhaupt noch Sinn machen. Je nachdem wie weit die Spanne zwischen technologischem Vorteil und Kostenreduktion aufgeht, wird das ganze früher oder später zum Problem werden.

Zuerst wird dies sicherlich AMD und nVidia bei ihren Grafikchips betreffen, da hierbei regelmäßig die herstellbaren Produktionsgrößen von Chips (derzeit durch die vorhandene Maskentechnik bei 600-700mm²) nahezu voll ausgereizt werden. Übliche PC-Prozessoren sind hingegen weit weniger groß (Intels Vierkerner liegen unter der 14nm-Fertigung bei lachhaften 122mm²), während die teilweise wirklich großen Server-Prozessoren zu gänzlich anderen Preislagen verkauft werden, wo sich das ganze also trotzdem noch rechnet. Der Effekt ist aber sowieso eher ein langsamer, schleichender – was man als kleinen Pluspunkt mitnehmen darf, denn den großen Knall, wo dann das plötzliche Ende der Entwicklung erreicht ist, wird es somit nicht geben. Alle Chipdesigner, Chipfertigung und Marktteilnehmer werden an diese Problematik eher langsam herangeführt, womit man dann je nach Situation entscheiden kann, ob die neuere Fertigung noch Sinn macht, ob man bei der maximalen Chipfläche heruntergehen muß oder ob ein höherer Abgabepreis noch marktverträglich ist.