Hauptlinks

Suchen

nVidia gibt Details zum AD102-Chip und zur Ada-Lovelace-Architektur bekannt

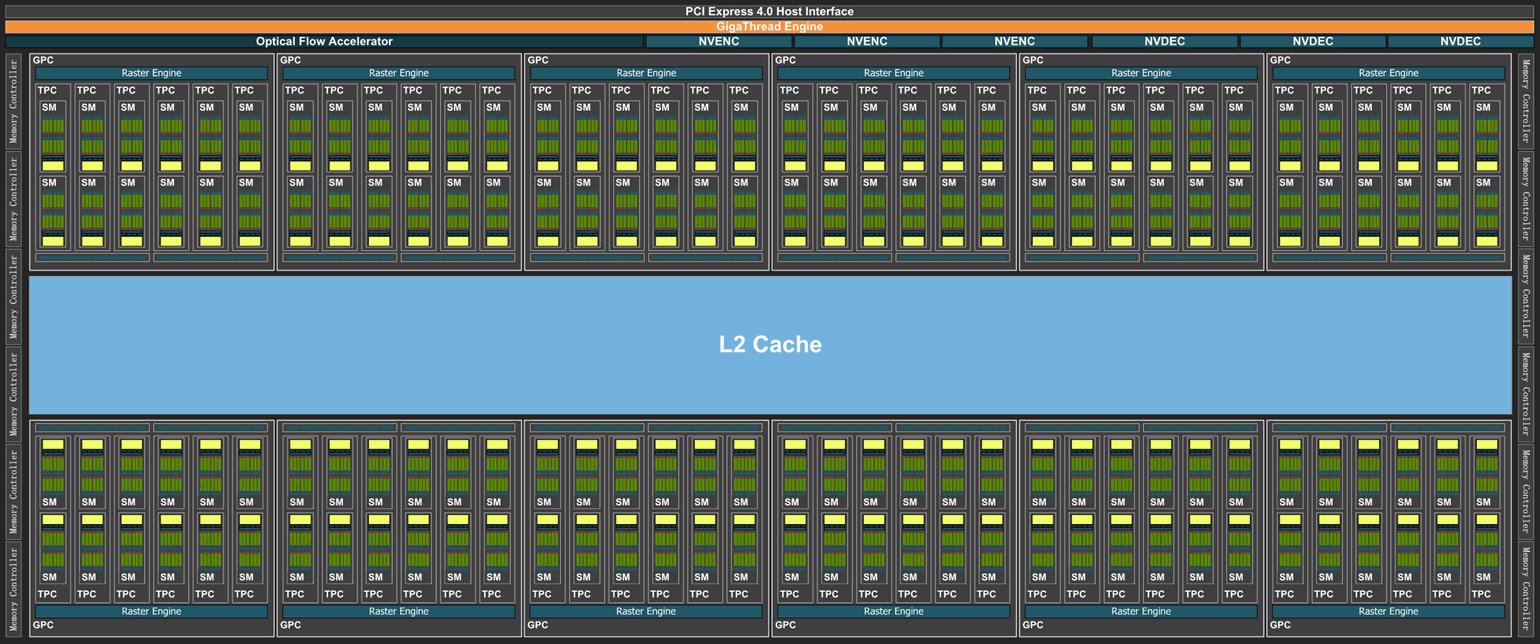

nVidia hat auf einem "RTX 40 Editors Day" genauere Details zur Ada-Lovelace-Architektur, dem AD102-Chip sowie zum "Founders Edition" Design der GeForce RTX 4090 bekanntgegeben. Leider nichts gesagt wurde zu den weiteren Ada-Grafikchips, wobei wenigstens die Verwendung von "AD103" für die GeForce RTX 4080 16GB sowie von "AD104" für die GeForce RTX 4080 12GB bestätigt wurde. Allerdings gab es einige Klarstellungen zu den noch offenen Fragen rund um die neue Grafikchip-Architektur – bei welcher sich im Gegensatz zur offiziellen RTX40-Vorstellung auch deutliche Abweichungen zu den bisher in der Gerüchteküche gehandelten Architektur-Daten ergeben. In dieser wurde die Ada-Lovelace-Architektur seit einiger Zeit mit einer deutlichen Veränderung der Shader-Cluster hin zu zusätzlichen INT32-Einheiten gehandelt, woraus sich ein beachtbarer Performance-Boost ergeben sollte.

|

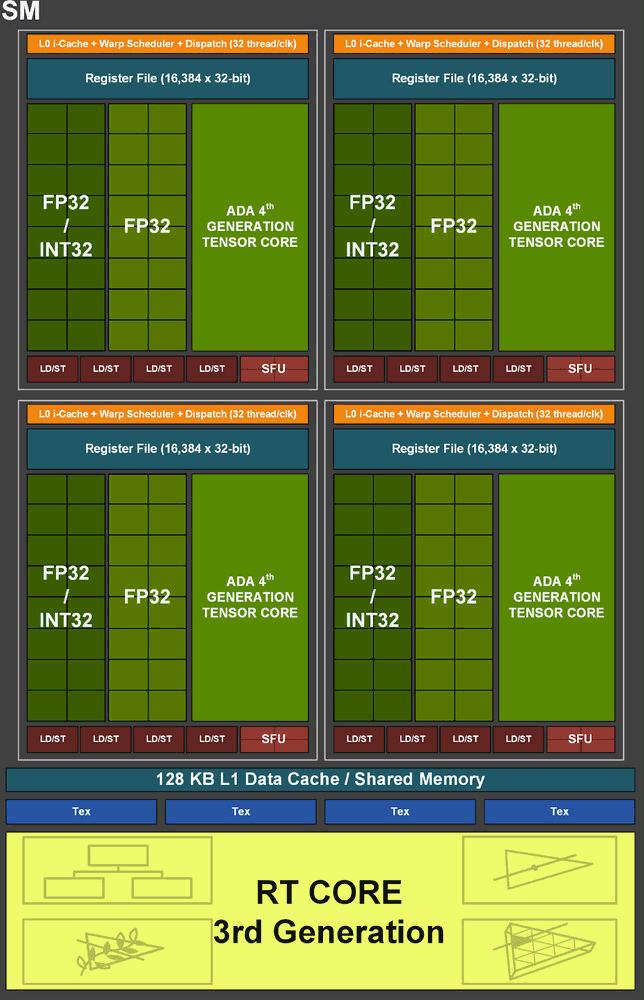

Dies wurde allerdings falsch von der Gerüchteküche vorhergesagt, laut den nVidia-Unterlagen ist der grundsätzliche Aufbau der Shader-Cluster zwischen "Ampere" und "Ada Lovelace" identisch. Auch andere Details der Gerüchteküche waren (leider) nicht korrekt: So gibt es weder mehr Level1-Cache pro Shader-Cluster noch gleich 32 ROPs pro Raster-Engine – es sind vielmehr 16 ROPs pro Raster-Engine, wie schon bei der Ampere-Architektur. Die ROP-Menge steigt somit nur mit der Anzahl der Raster-Engines (GPC) – was beim AD102-Chip stattlich aussieht, aber bei den anderen Ada-Chips dann natürlich deutlich kleiner ausfällt. Nachdem es anfänglich nur die nebulöse Aussage von "deutlich mehr Level2-Cache" zu eben selbigen gab, konnte inzwischen nachträglich bestätigt werden, dass der AD102-Chip im Vollausbau 96 MB Level2-Cache trägt – von welchem bei der GeForce RTX 4090 dann 72 MB freigeschalten sind.

Der relevante Punkt der ganzen Ausführungen liegt darin, dass "Ada Lovelace" somit der durch die Gerüchteküche vermutete deutliche Performance-Schwung aus den Shader-Clustern heraus fehlt. Eine Architektur mit (weiteren) 64 INT32-Einheiten kann für eine Durchsatz-Steigerung um immerhin +36% stehen, selbst nach Abzug üblicher Skalierungs-Verluste wäre dies ein gewichtiger Faktor in der Performance-Rechnung gewesen. In diesem Punkt hat sich die Gerüchteküche (leider) maßgeblich geirrt – nachdem "Ada Lovelace" in vielen anderen Punkten hingegen nahezu perfekt vorhergesagt wurde. nVidia hat dafür andere Punkte zur Steigerung des Rechen-Durchsatzes angebracht, aber keiner davon ist derart griffig wie extra INT32-Einheiten (welche natürlich auch Transistoren kosten würden, nVidia hat dies sicherlich exakt durchkalkuliert).

Letztlich passt dieses "fehlende" Feature jedoch um einiges besser zu den sich nunmehr langsam aus dem Nebel von nVidias Marketing lichtenden Performance-Punkten. Jene sehen ohne den Einfluß von DLSS die GeForce RTX 4090 derzeit um ca. 50-70% vor einer GeForce RTX 3090 Ti. Gegenüber gleich drei Performance-Bringern in Form von höherer Anzahl an Shader-Clustern (+52%), höherem Takt (nominell +36%) und stärkeren Shader-Clustern (+36% mehr Durchsatz angenommen extra INT32-Einheiten) erscheint dies trotz großzügigem Abzugs von Skalierungs-Effekten als deutlich zu mager. Rechnet man hingegen ohne den stärkeren Shader-Clustern allein mit höherer Anzahl selbiger plus dem Mehrtakt, dann ist ein solches Performance-Ergebnis zumindest denkbar – wenngleich es gern auch etwas höher ausfallen kann, der Rohleistungs-Gewinn zwischen GeForce RTX 3090 Ti und 4090 liegt immerhin bei +106%.

Zumindest wird die Performance-Kalkulation zwischen den GeForce RTX 30 & RTX 40 Serien ohne große Veränderungen in den Shader-Clustern somit einfacher: Zu beachten sind Anzahl der Shader-Cluster sowie die Taktraten, bezüglich letzterer kann man auch einfach mit der Faustregel "+45%" rechnen (trifft auf Vergleiche zur GeForce RTX 3090 Ti wegen deren hochgesetztem Boost-Takt nicht ganz zu). Da der Gewinn an Shader-Clustern bei den kleineren Ada-Lovelace-Modellen immer mehr abnimmt, bleibt im breiten Portfolio mehr oder weniger alles am Mehrtakt der Ada-Lovelace-Generation hängen. Aus technologischer Sicht erweist sich "Ada Lovelace" damit eher denn als "Ampere auf Stereoiden": Rein Architektur-seitig wurde vergleichsweise wenig verändert, dafür gibt es an der Spitze ein klar breiteres Design samt den Feature-Erweiterungen. Als hauptsächlicher Performance-Bringer quer durchs Chip-Portfolio agiert somit "nur" der durch den Wechsel auf Chipfertiger TSMC gewonnene Mehrtakt.

| Hardware | FP32 | Interface | L2-Cache | Speicher | PCI Express | Vorgänger | |

|---|---|---|---|---|---|---|---|

| AD102 | 12 GPC, 144 SM, 192 ROPs | 18'432 | 384 Bit | 96 MB | 24 GB | PCIe 4.0 x16 | GA102: 7 GPC, 84 SM @ 384 Bit, 6 MB L2 |

| AD103 | 7 GPC, 84 SM, 112 ROPs | 10'752 | 256 Bit | 64 MB | 16 GB | PCIe 4.0 x16 | GA103: 6 GPC, 60 SM @ 320 Bit, 4 MB L2 |

| AD104 | 5 GPC, 60 SM, 80 ROPs | 7680 | 192 Bit | 48 MB | 12 GB | PCIe 4.0 x16 | GA104: 6 GPC, 48 SM @ 256 Bit, 4 MB L2 |

| AD106 | 3 GPC, 36 SM, 48 ROPs, | 4608 | 128 Bit | 32 MB | 8 GB | PCIe 4.0 x8 | GA106: 3 GPC, 30 SM @ 192 Bit, 3 MB L2 |

| AD107 | 3 GPC, 24 SM, 32 ROPs | 3072 | 128 Bit | 32 MB | 8 GB | PCIe 4.0 x8 | GA107: 2 GPC, 20 SM @ 128 Bit, 2 MB L2 |

| Anmerkung: Angaben zu noch nicht vorgestellter Hardware basieren auf Gerüchten & Annahmen | |||||||

Nachtrag vom 22. September 2022

Um es gegenüber der kürzlichen Meldung mit den Chip-Daten zum AD102-Chip nochmals plastischer zu machen: Die wichtigen Innereien der Shader-Cluster der Ada-Lovelace-Architektur sehen exakt so wie bei der Ampere-Architektur aus. Die vorherige Gerüchteküche war zu diesem Punkt schlicht falsch – wobei sich jenes Gerücht auch nicht all zu weit verbreitete, da für die meisten wohl zu technisch angelegt. Wichtig ist der Punkt, dass sich hieran auch die ganz hohen Performance-Prognosen ergeben haben – welche somit obsolet sind. Gerechnet von GeForce RTX 3090 auf 4090 wäre inklusive einer Shader-Cluster-Verbesserung durchaus die dreifache effektive Rohleistung möglich gewesen. Die Nichtexistenz jener Shader-Cluster-Verbesserung drückt die Rohleistungs-Verbesserung (in diesem konkreten Beispiel) auf +120%.

| Pascal | Turing | Ampere | ADA (Gerücht) | ADA (real) | |

|---|---|---|---|---|---|

| reine FP32-Einheiten pro SM | 128 | 64 | 64 | angeblich 128 | 64 |

| reine INT32-Einheiten pro SM | - | 64 | - | angeblich 64 | - |

| Dual-Use FP32/INT32-Einheiten pro SM | - | - | 64 | angeblich keine | 64 |

| insgesamte FP32-Einheiten pro SM | 128 | 64 | 128 | angeblich 128 | 128 |

| insgesamte INT32-Einheiten pro SM | - | 64 | 64 | angeblich 64 | 64 |

| insgesamte FP32/INT32-Einheiten pro SM | 128 | 128 | 128 | angeblich 192 | 128 |

| Level1-Cache pro SM | 96 kB | 96 kB | 128 kB | angeblich 192 | 128 kB |

Ähnlich hohe Werte sind jedoch generell nur zwischen GA102 und AD102 erreichbar, da es nur dort eine deutlich höhere Anzahl an Shader-Clustern gibt (+71%). Bei den kleineren Ada-Grafikchips geht es deutlich nach unten, jene sind zumeist weit entfernt von +120% mehr nomineller Rohleistung – einfach weil die Anzahl der Shader-Cluster nicht derart stark steigt wie beim AD102-Chip. Nachfolgende Tabelle soll dies wiedergeben, ist aber natürlich inperfekt, da nur auf dem Vollausbau der jeweiligen Grafikchips sowie mit einheitlicher Taktrate kalkuliert. In der Praxis können die realen Grafikkarten wegen unterschiedlich starker Beschneidungen sowie hier und da höherer/niedriger Taktrate durchaus beachtbar von diesen Werten abweichen. Das zugrundliegende Prinzip sollte allerdings erkennbar sein: Den vollen Ada-Schub kann es nur an der Leistungsspitze geben, da die Hardware-Differenz mit den kleineren Ada-Chips immer geringer ausfällt.

| Ampere | Ada Lovelace | Rohleistungsgewinn (Vollausbau) |

|---|---|---|

| GA102 (84 SM) | AD102 (144 SM) | +71% SM, +47% Takt = +151% |

| GA103 (60 SM) | AD103 (84 SM) | +40% SM, +47% Takt = +106% |

| GA104 (48 SM) | AD104 (60 SM) | +25% SM, +47% Takt = +84% |

| GA106 (30 SM) | AD106 (36 SM) | +20% SM, +47% Takt = +76% |

| GA107 (20 SM) | AD107 (24 SM) | +20% SM, +47% Takt = +76% |

| benutzte Taktraten für diese Beispielrechnung: 1.7 (Ampere) & 2.5 GHz (Ada) | ||

Verwandte News

- Gerüchteküche: Termine der Launch-Reviews zu GeForce RTX 5080 & 5090, Radeon RX 9070 (XT) hingegen bewußt verzögert

- Eine (fehlbare) Performance-Prognose zur GeForce RTX 50 Serie

- nVidia auf der CES 2025: Vorstellung der GeForce RTX 50 Desktop- & Laptop-Serien

- Gerüchteküche: GeForce RTX 5080 mit 360W TDP, GeForce RTX 5090 mit 575W TDP

- Neuer Artikel: Das Hardware-Jahr 2025 in der Vorschau

- Umfrage-Auswertung: Aus welcher Generation stammt die zum Spielen benutzte Grafiklösung (2024)?

- Gerüchteküche: Die Spezifikationen zu GeForce RTX 5070 & 5070 Ti

- Die Grafikchip- und Grafikkarten-Marktanteile im dritten Quartal 2024

- Gerüchteküche: GeForce RTX 5070 Ti soll auf GB203-Basis mit 70 Shader-Clustern antreten

- Neuer Artikel: Grafikkarten-Verkaufsstatistik Mindfactory Q3/2024