Hauptlinks

Suchen

AMDs Zen 2 kommt im Chiplet-Design und mit verdoppelter FPU

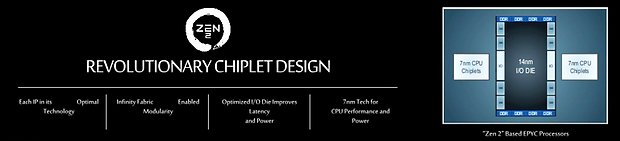

Auf AMDs "Next Horizon" Event hat der Chipentwickler die im nächsten Jahre antretende Zen-2-Architektur in gewissen Grundzügen vorgestellt. Der sicherlich markanteste Punkt ist dabei die Aufteilung des Prozessors in einzelne Chiplets – womit sich ein kürzliches Gerücht dann doch als wahr erweist. Dabei lagert AMD alle I/O-Funktionalität in einen extra Chip aus, die eigentlichen Prozessoren-Dies werden also um Chipsatz-Funktionalität, PCI Express und Speicherinterface befreit, tragen neben den CPU-Kernen samt dazugehörigem Cache wahrscheinlich also nur noch ein Infinity-Fabric-Interconnect zur Kommunikation untereinander. Damit ist AMD besser in der Lage, zielgenauere Kombinationen zu erstellen, verzichtet aber auf den (nicht unerheblichen) Verschnitt der bisherigen MultiChip-Lösungen (mehrfache I/O-Einheiten in allen Einzel-Dies, welche dann nur teilweise genutzt werden). Mit dem neuen Ansatz muß nur noch das hergestellt werden, was wirklich benötigt wird – und kann man auch je nach Bedarf mit kleinen oder größeren I/O-Einheiten experimentieren. Als Bonus oben kommt die I/O-Einheit weiterhin (kostengünstig) aus der 14nm-Fertigung, nur die eigentlichen "Core-Chiplets" kommen aus der 7nm-Fertigung von TSMC.

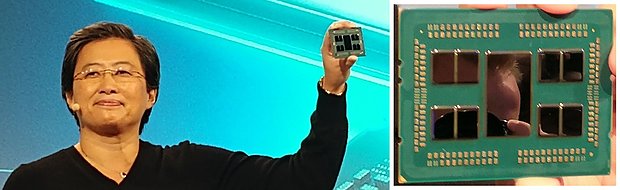

AMD Next Horizon 2018 Präsentation: Zen 2 64-Kern-Serverchip (Original-Bilder © AnandTech: #1 & #2)

Selbige Core-Chiplets tragen dann im Server-Bereich jeweils 8 CPU-Kerne, womit bei der Maximal-Konfiguation mit 64 CPU-Kernen pro Sockel also 8 Core-Chiplets sowie die obligatorische I/O-Einheit zum Einsatz kommen. Damit könnte man dieses Schema durchaus auch im Desktop-Bereich bei den Ryzen-Prozessoren verwenden: Ein 12-Kerner aus der Ryzen 3000 Serie würde dann eine I/O-Einheit tragen (logischerweise eine andere, kleinere als im Server-Bereich verwendet) sowie zwei Core-Chiplets mit physikalisch 16 CPU-Kernen, von welchen man nur 12 Stück für diesen Prozessor aktiviert. Selbst bei einem Achtkern-Prozessor ist der ganze Ansatz noch nicht wirklich ineffizient, da ja dann lediglich die I/O-Einheit ausgelagert ist, aber nichts in irgendeiner Form doppelt existiert. Nur im APU-Bereich dürfte man mit einem monolithischen Ansatz weiterhin besser kommen, da dort dann schließlich auch noch eine Grafikeinheit integriert werden muß und keine besondere Skalierung (wie im Server-Bereich) notwendig wird. Trotzdem ist das Chiplets-Modell derzeit nur für Epyc und damit indirekt auch für Threadripper gesichert, bei Ryzen jedoch nur eine der vorhandenen Möglichkeiten.

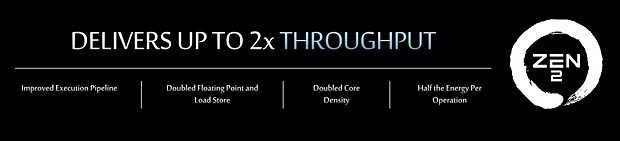

Für alle diese Zen-2-Derivate gelten natürlich die Architektur-Verbesserungen von "Zen 2" gemeinschaftlich, welche AMD mittels einiger Stichworte angeschnitten hat. Markant sind hierbei die Verbesserungen am Frontend, welches zur besseren Fütterung der Ausführungseinheiten mit Befehlen dient, sowie die neue Floating-Point-Einheit (FPU), welche nun (anstatt 4x 128 Bit) gleich 4x 256 Bit breit ist. 256-Bit-Befehle konnte zwar auch schon das Zen-1-Design ausführen, dies jedoch nur unter Kopplung zweier FPUs, also bei halbierter Performance – dies entfällt nunmehr und unter den passenden Befehlen kann sich der FPU-Durchsatz von Zen 2 ergo verdoppeln. Eine exakte Angabe zur verbesserten IPC blieb AMD allerdings derzeit noch schuldig – wobei dies zu diesem frühen Zeitpunkt vielleicht noch nicht sein muß, bis zum praktischen Einsatz von Zen 2 gehen sicherlich noch einige Monate ins Land.

Primär wieder zugunsten des Server-Einsatzes gemeint sind dagegen die Anmerkungen über verdoppelte Kern-Anzahl ("Double Core Density") und verdoppelte Energieeffizienz ("Half the Energy per Operation"). Im Server-Bereich wurden bis zu 64 CPU-Kerne (pro Sockel) bei den Zen-2-basierten Epyc-Prozessoren nochmals bestätigt, selbiges ist für das Desktop-Segment dagegen noch einigermaßen offen. Und die Energieeffizienz geht natürlich Kern- und Taktraten-normalisiert deutlich nach oben, dafür sorgt allein die 7nm-Fertigung. Doch in der Praxis wird AMD diese freiwerdenden Reserven im Server-Segment durch die genannte verdoppelte Kern-Anzahl sowie im Desktop-Segment vermutlich auch über mehr CPU-Kerne samt höheren Taktraten wieder egalisieren. Die reine Energieeffizienz der Zen-2-Prozessoren wird natürlich auch weiterhin steigen, aber deren insgesamte Leistungsaufnahme deswegen nicht oder bestenfalls nur geringfügig sinken. Es lohnt sich für AMD an dieser Stelle einfach nicht, mögliche Performance nur wegen niedrigerer TDP-Angaben liegen zu lassen, ergo dürfte man auch die neuen Prozessoren so weit ausfahren, wie es übliche TDP-Größen zulassen.

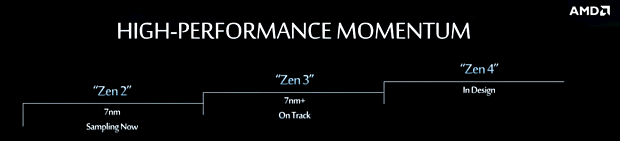

Terminlich hatte man leider nicht viel mehr als "2019" zu sagen. Allgemein erwartet man die Server-Prozessoren der Zen-2-Generationen diesesmal als Vorreiter, da AMD mit diesen Intel am meisten weh tun kann, und gleichfalls das langsame Anfahren der 7nm-Fertigung bei den dort benötigten Stückzahlen am wenigsten auffällt. Die Zen-2-Vorstellung für Server darf demzufolge noch im ersten Halbjahr erwartet werden, vermutlich irgendwann im zweiten Quartal. Zen-2-basierte Desktop-Prozessoren werden dann erst nachfolgen können, wenn die 7nm-Fertigung bei TSMC ausreichend für diesen viel höheren Bedarf läuft, sprich kaum vor dem Sommer 2019. Davon abgesehen arbeitet man bei AMD-intern natürlich schon längst an entsprechenden Nachfolgern und hatte demzufolge abschließend auch noch eine Architektur-Roadmap parat, welche erstmals die Zen-4-Generation offiziell nennt. Zu jener existiert noch kein Termin und es wurde auch kein Fertigungsverfahren genannt, vermutlich kann man in den Jahren 2021/22 dann aber schon TSMCs 5nm-Prozeß nutzen.

Nachtrag vom 6. November 2018

Zu betonen sei bezüglich AMDs Chiplet-Ansatz bei Zen 2 nochmals der Punkt, das dies eine bislang für Ryzen und damit Consumer-CPUs unbestätigte Sache ist – und selbst im Fall des Falles etwas abweichend vom vorgestellten Server-Modell kommen dürfte. Dort setzt AMD auf eine vergleichsweise riesige I/O-Einheit, resultierend aus dem enormen Chipsatz-Kapazitäten im Server-Bereich (8-Kanal-Speicherinterface samt 128 PCI Express 4.0 Lanes) und der zugrundeliegenden 14nm-Fertigung. Im übrigen liegt genau an dieser Stelle auch ein weiterer Grund für diese Aufteilung zwischen I/O-Einheit und Core-Chiplets: Das allermeiste, was in der I/O-Einheit liegt, skaliert vergleichsweise schlecht mit kleineren Fertigungsverfahren – dies betrifft insbesondere Interface, deren Flächenvorteil unter einer kleineren Fertigung in aller Regel nur mittelprächtig ist. Dies in der teuren 7nm-Fertigung in einen monolithischen Chip zu bringen, würde selbigen vergleichsweise groß und teuer machen – so fertigt AMD nunmehr nur noch das unter 7nm, was richtig gut skaliert und auch von den Energieverbrauchs-Eigenschaften der 7nm-Fertigung bestmöglich profitiert (sprich die Core-Chiplets). Somit kommt hierbei eben nur noch ein einzelnes 7nm-Die (mit 8 CPU-Kernen) heraus, welches mit geschätzt ~73mm² vergleichsweise klein ausfällt und daher bei TSMC mit wohl exzellenter Ausbeute (selbst in den Anfängen der 7nm-Fertigung für PC-Produkte) hergestellt werden kann.

Unter Desktop-Bedingungen wird dann allerdings nicht die mit geschätzt ~430mm² regelrecht riesige I/O-Einheit benötigt, sondern etwas viel kleineres – insofern wird es nicht dazu kommen, das man im Desktop-Bereich diese riesige I/O-Einheit mit nur einem einzelnen Core-Chiplet koppelt (was etwas komisch aussehen würde). Eher denkbar wäre für den Desktop-Bereich eine separate I/O-Einheit mit DualChannel-Speicherinterface und sagen wir 24 PCI Express 3.0 Lanes (oder auch schon Version 4.0), jene kann dann bei grob einem Drittel der Fläche der I/O-Einheit der Server-Prozessoren liegen. Dazwischen dürfte AMD eine mittlere I/O-Einheit für Threadripper positionieren, denn auch dort sind die Anforderungen wiederum anders: QuadChannel-Speicherinterface samt 32 PCI Express 4.0 Lanes, was auf etwas mehr als der Hälfte der Fläche der I/O-Einheit der Server-Prozessoren als lösbar erscheint. Denkbar sind hier natürlich noch andere Rechnungen – beispielsweise den Einschluß einer kleinen Grafiklösung bei der I/O-Einheit für Desktop-Prozessoren. Denkbar ist genauso auch noch, das es im Desktop-Bereich dennoch wieder zu einem extra monolithischen Die kommt – mit wie gesagt dem Nachteil, das man dann auch schlecht skalierende Chipteile unter der teuren 7nm-Fertigung auflegt. Im APU-Bereich wird dies wahrscheinlich am Ende dennoch so gemacht werden – aber Zen-2-basierte APUs stehen wohl auch nicht mehr für das Jahr 2019 an, sondern dürften erst Anfang 2020 als Nachzügler erscheinen.

| AMD Zen 2 | I/O-Einheit | Core-Chiplets | Chipfläche | Status |

|---|---|---|---|---|

| Epyc 64-Kern-Chip | große I/O-Einheit (8Ch. DDR4, 128 PCI Express 4.0 Lanes) á ~430mm² | 8x Core-Chiplets á ~73mm² | ~1014mm² | offiziell vorgestellt |

| Threadripper 32-Kern-Chip | mittlere I/O-Einheit (4Ch. DDR4, 32 PCI Express 4.0 Lanes) á ~260mm² | 4x Core-Chiplets á ~73mm² | ~552mm² | anzunehmen |

| Ryzen 16-Kern-Chip | kleine I/O-Einheit (2Ch. DDR4, 24 PCI Express 3.0 Lanes) á ~160mm² | 2x Core-Chiplets á ~73mm² | ~306mm² | spekulativ |

| Ryzen 8-Kern-Chip | kleine I/O-Einheit (2Ch. DDR4, 24 PCI Express 3.0 Lanes) á ~160mm² | 1x Core-Chiplet á ~73mm² | ~233mm² | spekulativ |

| APU | monolithischer Ansatz mit möglicherweise 6 CPU-Kernen, Navi-iGPU, 2Ch. DDR4 & 12 PCI Express 3.0 Lanes | ? | spekulativ | |

Der insgesamte Vorteil dieses Chiplet-Ansatzes liegt in der höheren Flexibilität und damit dem geringeren Verschnitt für die einzelnen Produkte. Bislang musste AMD in seine Zen-Dies immer alles an I/O-Kapazitäten einbauen, was maximal benötigt wird – deswegen tragen die im Ryzen-Bereich verwendeten Dies auch ihre Infinity-Fabric-Verbindungen, obwohl jene dort nicht genutzt werden. Mit steigender Anzahl an benutzten Dies wird zudem viel Chipsatz-Funktionalität mehrfach (sinnlos) verbaut – und wenn man an irgendeiner Stelle nachlegen wollte, würde dies immer das gesamte Produktspektrum von Epyc bis Ryzen 3 betreffen. Mit dem neuen Ansatz kann AMD die I/O-Kapazitäten zielgenau auflegen, wäre theoretisch sogar zu Sonderlösungen in der Lage oder könnte den Support für DDR5 und PCI Express 5.0 basierend auf derselben Architektur-Stufe einfach nachreichen, ohne an den eigentlichen Core-Chiplets etwas verändern zu müssen. Der Ansatz ist sicherlich komplizierter, aber auch effektiver und flexibler – was bei größeren Stückzahlen vermutlich einfach zugunsten einer besseren Wirtschaftlichkeit geht. Zudem wird über die I/O-Einheit in der 14nm-Fertigung auch der Hausfertiger GlobalFoundries weiterhin eingebunden, was helfen wird, dessen Überleben nach dem Schritt in die (technologisch) zweite Reihe zu sichern.

Nachtrag vom 7. November 2018

Bezüglich AMDs Chiplet-Ansatz bei Zen 2 tobt derzeit natürlich die Diskussion darüber, wie Zen-2-basierte Ryzen-Prozessoren aussehen werden bzw. ob jene tatsächlich auch in diesem Chiplet-Design erstellt sind. Wie gestern schon ausgeführt, ist dies durchaus denkbar – die andere Auflösung eines weiterhin monolithischen Designs für "Ryzen 3000" (Codename "Matisse") ist jedoch auch weiterhin eine sehr gute Möglichkeit. Im Anwendungsbereich dieser Prozessoren wäre das Chiplet-Design bei weitem nicht mehr so effektiv wie bei den großen Workstation- und Server-Prozessoren, zudem geht im Chiplet-Design dann auch die direkte Speicheranbindung und damit Spiele-Performance verloren – ein Schicksal, welches man sich derzeit schon teilweise bei den Spiele-Benchmarks zu AMDs Threadripper-Prozessoren ansehen kann (welche in dieser Frage klar hinter den normalen Ryzen-Prozessoren zurückliegen). Sicherlich ist Spiele-Performance bei Desktop-Prozessoren auch nicht alles und könnte AMD sich neue Gegenmaßnahmen hier gegenüber einfallen lassen – doch würde man damit in jedem Fall eine sehr große Flanke gegenüber Intel offenlassen.

Hinzu kommt, das sich derzeit die Betrachtung von Consumer-Prozessoren durch die Prozessoren-Käufer zu verändern scheint: Anwendungs-Benchmarks wird immer weniger Gewicht eingeräumt, viele schauen einfach nur noch auf die Spiele-Benchmarks neuer PC-Prozessoren. Dies hängt weniger mit besonders großen Differenzen im Spiele-Bereich zusammen (welche dort sogar bemerkbar geringer ausfallen), sondern vielmehr mit einer gewissen Sättigung an Anwendungs-Performance, zumindest bei einem CPU-Neukauf. Man kann also bei einer erklecklichen Anzahl an CPU-Käufern mit der Anwendungs-Performance glänzen wie man will – ohne eine konkurrenzfähige Spiele-Performance hat man da keine Chance. Mit einem Chiplet-Design auch bei Ryzen 3000 würde AMD also einen fundamentalen Nachteil zementieren, welchen man auch über Architektur-Verbesserungen und Mehrtakt schwerlich jemals wieder egalisieren kann. Da wie gesagt die Effizienzvorteile des Chiplet-Designs bei kleineren Prozessoren immer geringer ausfallen, wäre Ryzen 3000 als monolitisches Design durchaus auch eine sinnvolle Auflösung – selbst wenn man damit auf die Möglichkeit verzichtet, sehr einfach bei der Kern-Anzahl skalieren zu können. Aber womöglich reicht AMDs Absatz inzwischen auch aus, um wieder mehrere Dies pro CPU-Generation aufzulegen – beispielsweise monolitische 8-Kerner und 12-Kerner für Ryzen sowie einen 6-Kerner für den APU-Bereich.

Dies hängt sicherlich auch stark von der Frage ab, wieviele CPU-Kerne sich AMD in den jeweiligen Marktsegmenten nun wirklich vorstellt. Klar ist, das im Zen-2-Zeitalter Epyc II mit bis zu 64 CPU-Kernen sowie Threadripper 3000 mit bis zu 32 CPU-Kernen antreten werden. In diesem beiden Marktfeldern sind mehr CPU-Kerne auch keinerlei Problem, sondern vielmehr ein entscheidendes Verkaufsargument. Bei den Desktop-Prozessoren funktioniert diese Verkaufsargumentation zwar auch teilweise, allerdings kommt man mit steigender Kern-Anzahl auch in Auslastungs-Probleme unter typischer Desktop-Software oder aber in die Zwickmühle, das Prozessoren mit mehr CPU-Kernen niedrigere Taktraten provozieren und damit unter gewissen Szenarien sogar langsamer herauskommen. Gut möglich also, das AMD von (gerüchteweiser) früheren Planungen abrückt, auf dem Sockel AM4 mit der Zen-2-Generation gleich bis zu 16 CPU-Kerne aufzubieten – und erst einmal etwas behutsamer herangeht. Auf der richtigen Taktrate und mit der richtigen IPC ist ein Desktop-Achtkerner eine feine Sache, da dürften es 10- und 12-Kerner schwer dagegen haben, weil (auf gleicher TDP) kaum noch wirklich schneller zu bekommen. Wie genau AMDs Pläne bei Ryzen 3000 aussehen, muß sich allerdings erst noch im Laufe der nächsten Monate ergeben – auf AMDs "Next Horizon" Event wurde schließlich nur die Zen-2-Architektur sowie daraus resultierende Epyc-Prozessoren besprochen.

Nachtrag vom 14. November 2018

AnandTech haben im Interview mit AMDs CTO Mark Papermaster noch einige interessante Details zu Zen 2 herauskitzeln können. So wurde bestätigt, das die I/O-Einheit aus der 14nm-Fertigung von GlobalFoundries kommt (und das Core-Chiplet aus der 7nm-Fertigung von TSMC) – womit AMD letztlich den kompletten Zen-2-Chip aus der Produktion zweier Chipfertiger mit sogar unterschiedlichen Nodes zusammensetzt. Das Core-Chiplet wird AMD-intern im übrigen als "Compute Die" (CCD) bezeichnet, ergo könnte man die I/O-Einheit demzufolge als "I/O Die" (IOD) benennen. Jene Computer Dies sind dann jeweils per Infinity Fabric mit dem I/O-Die verbunden, nicht allerdings CCD-intern verbunden – jeglicher Datenverkehr läuft generell über das I/O-Die ab. Daneben erwartet AMD vom Zen-2-Design mit seinem nominell verdoppelten FPU/AVX-Durchsatz dann auch keine Taktraten-Drosselung bei heftigem AVX-Einsatz, wie dies Intels Prozessoren größtenteils derart handhaben müssen. Hier könnte man natürlich die Vorteile der 7nm-Fertigung richtig ausnutzen – sprich, wenn Intel eines Tages auf der (für Intel) vergleichbaren 10nm-Fertigung angelangt ist, könnte Intel in dieser Disziplin entsprechend nachziehen.

Verwandte News

- Die Performance des Ryzen 7 1800X im Laufe der Zeit

- Ryzen 2000 Launchreviews: Die Testresultate zur Spiele-Performance im Überblick

- Ryzen 2000 Launchreviews: Die Testresultate zur Anwendungs-Performance im Überblick

- Die Systemanforderungen für die Spiele-Generation 2017/18

- Threadripper Launchreviews: Die Testresultate zur Anwendungs-Performance im Überblick

- AMD Ryzen 5 Launchreviews: Die Testresultate zur Spiele-Performance im Überblick

- AMD Ryzen 5 Launchreviews: Die Testresultate zur Anwendungs-Performance im Überblick

- Eine Performance-Prognose zum Ryzen 5 1600X Sechskern-Prozessor

- AMD Ryzen Launchreviews: Die Overclocking-Ergebnisse im Überblick

- AMD Ryzen Launchreviews: Die Testresultate zur Spiele-Performance im Überblick