Hauptlinks

Suche

nVidias "Denver" ARM-Cores sind 7fach skalar & sollen sich mit Haswell anlegen können

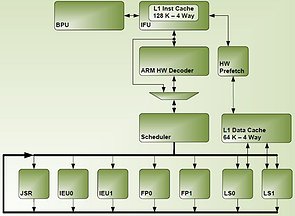

nVidia hat kürzlich in einem Blogposting weitere Details zur Architektur seines Projekts "Denver" bekanntgegeben, welche erstmals in den bald zu erwartenden Tegra K1 64-Bit-Prozessoren verbaut werden wird (die Tegra K1 32-Bit-Prozessoren basieren hingegen auf gewöhnlichen Cortex-A15-Rechenkernen und sind mit "Denver" überhaupt nicht zu vergleichen). Nunmehr wird auch klar, wieso nVidia bei Tegra K1 64-Bit mit nur Zweikern-Modellen die gleiche Performance erreichen will wie beim (schon erhältlichen) Tegra K1 32-Bit mit Vierkern-Modellen: Tegra K1 64-Bit kommt gleich 7fach skalar daher, hat also pro Rechenkern gleich sieben Ausführungseinheiten. Davon sind zwei Load/Store-Einheiten, welche sich also nur um Zwischenspeicherungen und nicht um die eigentliche Befehlsausführung kümmern, bleiben also (vermutlich) fünf echte Ausführungseinheiten übrig.

Dies ist ungewöhnlich viel für einen SoC-Prozessor: Cortex-A9, Cortex-A12 und Cortex-A53 werden als 2fach skalar angegeben, die schnelleren Cortex-A15 und Cortex-A57 als 3fach skalar (der Cortex-A15 tritt allerdings mit mindestens vier echten Ausführungseinheiten an, beim Cortex-A57 scheinen es ebenfalls fünf echte Ausführungseinheiten zu sein). In jedem Fall ist nVidias "Denver" ARM-Abwandlung somit viel näher an dem Design eines echten PC-Prozessors als am Design eines Smartphone/Tablet-SoCs – was nVidias Tegra K1 64-Bit damit natürlich auch wieder für die von nVidia angedachten höheren Aufgaben empfiehlt. Auch andere Detail-Optimierungen am Denver-Design stützen diesen Ansatz.

Ein zweites wichtiges Feature ist die Ausweitung des Code-Cachings unter dem Featurenamen "Dynamic Code Optimization". Den vorliegenden Microcode zu analysieren, zu optimieren und zwischenzuspeichern wird von allen modernen CPUs (inklusive ARM) beherrscht, nVidia gibt hier aber noch 128 MB vom Hauptspeicher als zusätzlichen Cache oben drauf. Damit können nicht mehr nur die wirklich am häufigsten benötigten Codeschnippsel in den nur Kilobyte-großen Caches der CPU zwischengespeichert werden, sondern ganze optimierte Programmcodes werden ständig im Hauptspeicher vorrätig gehalten. Die Idee ist angesichts heutiger Hauptspeicher-Größen generell interessant und könnte uns eventuell bei kommenden CPU-Architekturen anderer Chipentwickler wiederbegegnen.

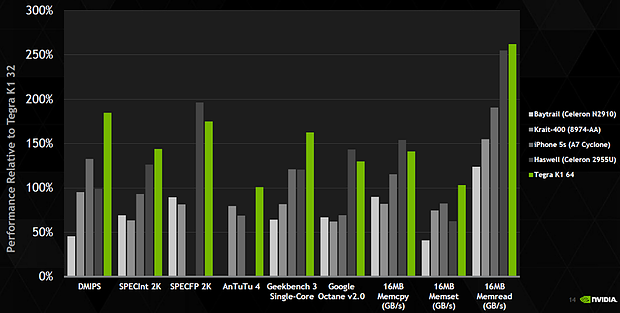

Um zu beweisen, was Tegra K1 64-Bit nun in der Lage ist zu leisten, hat nVidia zudem im Rahmen der HotChips-Konferenz einige Benchmarks veröffentlicht, welche das Denver-Produkt gegen typische Smartphone/Tablet-SoCs und aber auch gegen einen Haswell-Prozessor antreten lassen. Der dafür benutzte Celeron 2955U stellt allerdings mit nur zwei Rechenkernen (ohne HyperThreading) auf 1.4 GHz Takt das wirklich unterste Ende des Haswell-Portfolios dar, Intel hat da durchaus potentere Modelle mit sogar niedrigeren TDPs im Angebot. Einen gänzlich fairen Vergleich gibt es aber sowieso nicht, da Tegra K1 64-Bit wohl lüfterlos daherkommt und eine dementsprechend niedrige TDP haben dürfte, während alle Haswell-Prozessoren (inklusive der SoC-Modelle) zu hohe TDPs für einen lüfterlosen Einsatz aufweisen.

Trotzdem scheint es als bemerkenswert, was nVidia hier mit nur zwei Rechenkernen und auf sehr niedriger TDP erreicht: Denn wenn sich SoC-Prozessoren bisher mit echten PC-Prozessoren anlegen konnten, dann hatten die SoCs gewöhnlich die doppelte Anzahl an Rechenkernen, hier steht aber ein Vergleich auf gleicher Anzahl an Rechenkernen. Andererseits gilt auch, daß der von nVidia selber angegebene Performance-Abstand zu gebräuchlichen SoCs anderer Anbieter (welcher ungefähr beim Faktor 1,5 bis 2 liegt) eigentlich nicht ausreichend hoch ist für den üblichen Performance-Abstand zwischen Smartphone/Tablet-SoCs und PC-Prozessoren im Mobile-Einsatz (Richtung Faktor 3 und mehr). Man darf durchaus vermuten, daß sich nVidia mit diesen Benchmark-Zahlen ins bestmögliche Licht gestellt hat, daß die Realität dann aber doch noch ein wenig anders aussieht.

Verwandte News

- Tabletchip-Vergleich: nVidia Tegra 3 vs. Apple A5X

- nVidia verteilt Entwicklerkits für "Project Denver"

- AMD kündigt ARM-basierte LowPower-Prozessoren in Konkurrenz zu den eigenen x86-Designs an

- AMD bringt 2014 ARM- sowie Kaveri-basierte Server-Prozessoren

- AMD wird zukünftig ARM-basierte Prozessoren für den Microserver-Bereich entwickeln