Hauptlinks

Suchen

Grundsätzlicher Aufbau von AMDs Zen-Serverprozessoren offengelegt

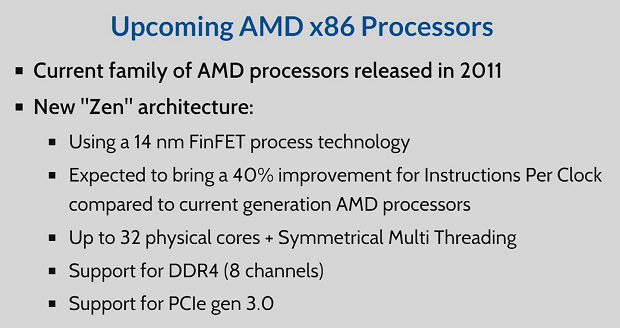

Aus einer beim CERN abgehaltenen Präsentation zu verschiedenen Entwicklungen im Serverbereich lassen sich einige Informationen zum grundsätzlichen Aufbau von AMDs Zen-Serverprozessoren ziehen – welche zudem augenscheinlich aus seriöser Quelle mit direktem Zugang zu AMD stammen und daher nahezu offiziellen Charakter haben dürften. Genannt bzw. bestätigt wurden dabei bis zu 32 CPU-Rechenkerne bei den Server-Modellen, welche Zugriff auf ein gleich achtkanaliges Speicherinterface haben werden, sowie die Nutzung von PCI Express bis zur Version 3.0 dieses Standards. Genannt wurde genauso die 14nm FinFET-Fertigung – was nur bei GlobalFoundries und Samsung (sowie theoretisch Intel) möglich ist, TSMC damit effektiv ausschließt (da TSMC sein aktuelles Herstellungsverfahren mit "16nm FinFET" benennt). Zudem wird der 40%ige Performancegewinn bei den "Instruction per Clock" (IPC) gegenüber AMDs aktuellen Prozessoren als Erwartung genannt, in dieser Frage dürfte man sich auf AMDs höchsteigene Aussage hierzu beziehen.

Die bis zu 32 CPU-Rechenkerne werden dabei allerdings nicht auf ein und demselben Prozessoren-Die erreicht, sondern durch eine Unterteilung in zwei Prozessoren-Dies mit je 16 CPU-Rechenkernen (welches jeweils ein einzelnes QuadChannel-Speicherinterface trägt) auf einem "Multi Chip Package" (MCM). Als Verbindung zwischen beiden Dies kommt offenbar ein Nachfolger des HyperTransports-Links zum Einsatz zum Einsatz kommen, welches gemäß früheren Gerüchten allerdings sehr viel mehr Bandbreite als HyperThransport bieten soll. In jedem Fall reduziert AMD damit die Die-Fläche von Zens Server-Versionen enorm, wenn das größte Die "nur" 16 Rechenkerne tragen wird – samt Interfaces und Level3-Caches dürfte da eine Chipfläche im Rahmen von 300-350mm² (je nach konkreter Menge des Level3-Caches) herauskommen. Ein Prozessoren-Die in dieser Größe dürfte deutlich einfacher und wirtschaftlicher herzustellen sein als ein Prozessoren-Die mit gleich 32 CPU-Rechenkernen und dann in Richtung 600mm² Chipfläche – hier liegt der Sinn der ganzen Übung.

Die Präsentation bezog sich allein auf Server-Entwicklungen – und ging damit nicht auf eventuelle Desktop-Modelle ein, welche wahrscheinlich hiervon abweichen werden. Schon allein aus Gründen der Wirtschaftlichkeit wird AMD ziemlich sicher im Desktop-Markt nicht einfach teildeaktivierte Server-Chips verwenden, sondern dafür einen nativen Achtkerner auflegen. Jener kann zudem dann auf ein einfaches DualChannel-Speicherinterface beschnitten werden, mehr ist im Desktop-Einsatz (gerade angesichts von DDR4) nicht vonnöten. Gleichfalls kann in einem solchen dedizierten Desktop-Chip die große Interconnect-Technik sowie eventuell auch ein gewisser Teil des Level3-Caches entfallen, welcher bei Desktop-Aufgaben in aller Regel nicht wirklich ausgenutzt wird. Ein solch nativer Achtkerner für den Desktop-Einsatz könnte dann bei einer Chipfläche von ~150mm² oder sogar etwas kleiner herauskommen, womit dann auch günstige Preispositionen einnehmbar sind (AMDs aktuelle Achtkern Desktop-Prozessoren belegen 315mm² Chipfläche in der 32nm-Fertigung).

Verwandte News

- AMD stellt den neuen Boxed-Kühler "Wraith" zusammen mit einer Preisanpassung für den FX-8370 vor

- AMD stellt drei Kaveri- und einen Carrizo-Prozessor für den Desktop vor

- Umfrage-Auswertung: Welche neue Hardware wird im Jahr 2016 am meisten erwartet?

- AMD aktualisiert seine Prozessoren- und Grafik-Roadmap für das Jahr 2016

- Microsoft schränkt den Prozessoren-Support für Windows 7/8 (rein offiziell) ein

- Neuer Artikel: Das Hardware-Jahr 2016 in der Vorschau

- Newegg-Ranking der meistverkauften Prozessoren und Grafikkarten 2015

- Feature- und Modelldaten zum Carrizo-Refresh "Bristol Ridge" aufgetaucht

- Die Systemanforderungen für die PC-Spiele 2015/2016

- Zen-Details: Vier Integer-Einheiten und vier 128-Bit Fließkomma-Einheiten pro CPU-Kern