Hauptlinks

Suchen

AMD arbeitet am technischen Unterbau von MultiChip-Grafiklösungen

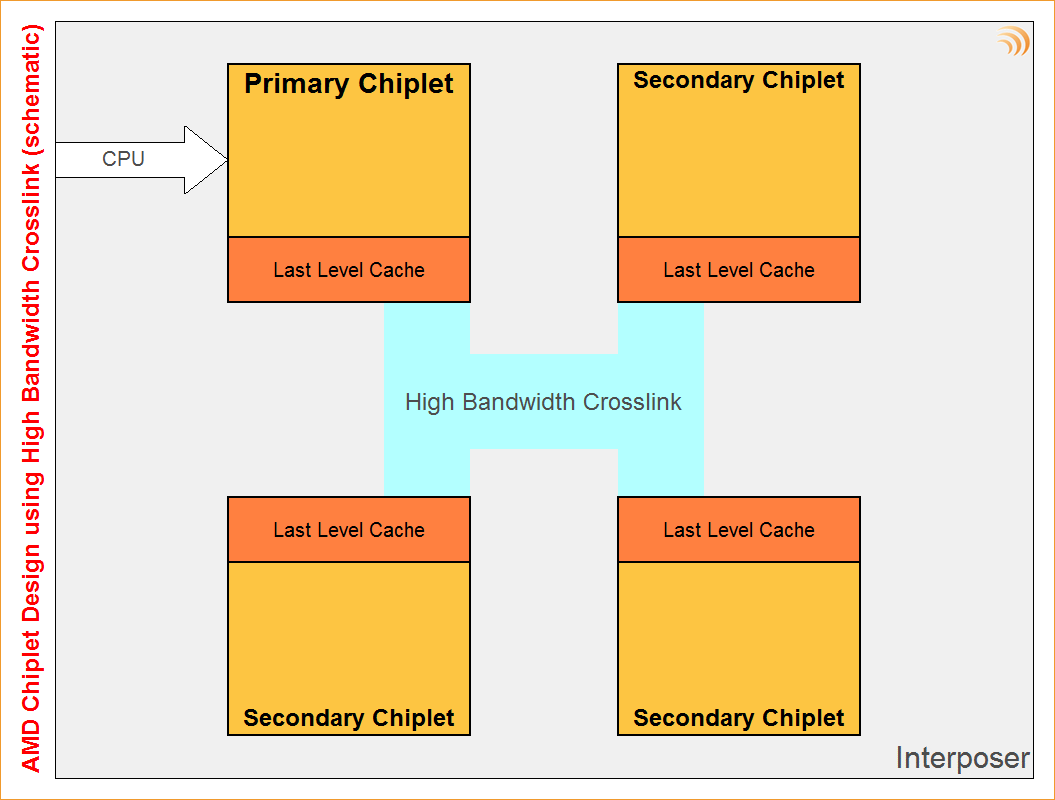

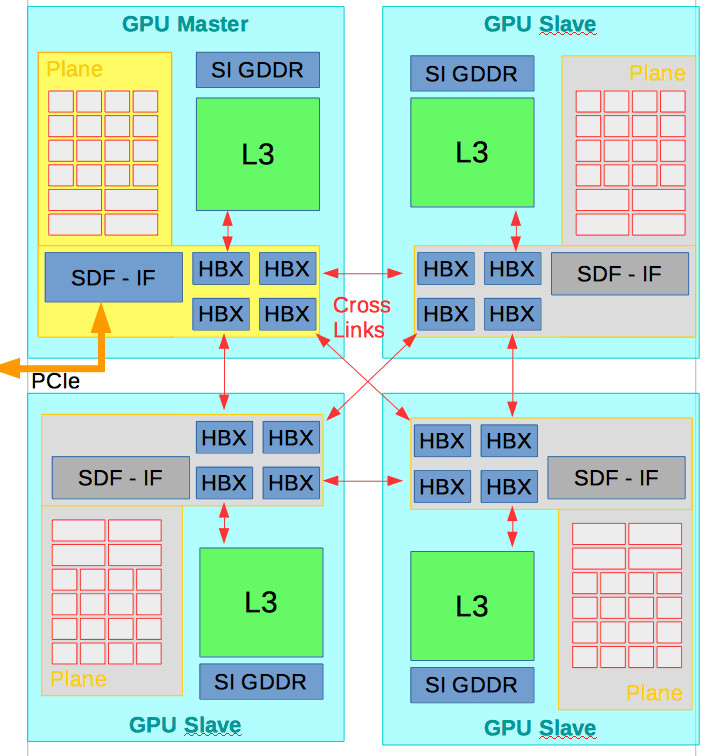

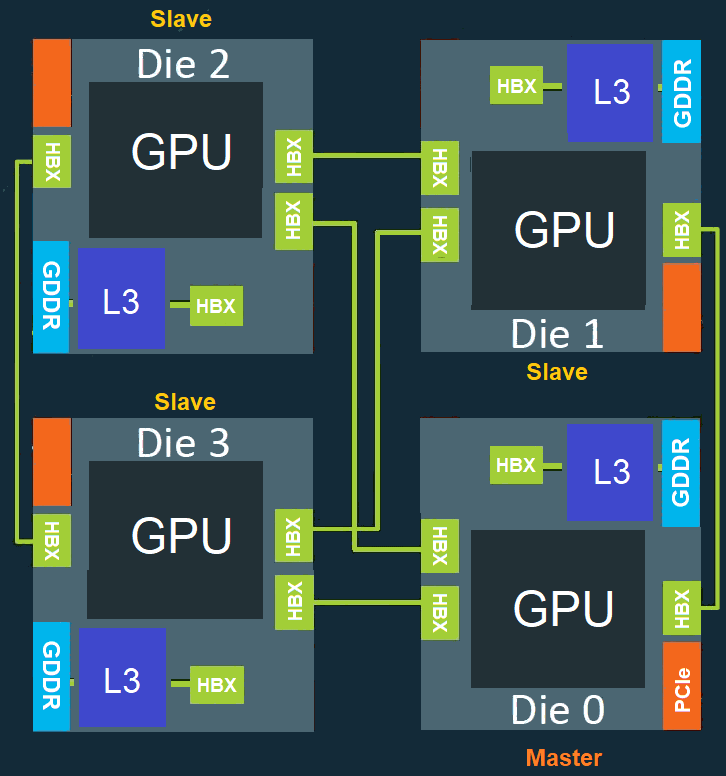

VideoCardz erwähnen ein hochinteressantes, neu eingereichtes AMD-Patent, welches von multiplen GPU-Chiplets spricht – und damit augenscheinlich den technischen Unterbau zu MultiChip-Lösungen im Grafikkarten-Bereich liefern soll. Die Patentschrift selber ist abstrakt genug gehalten, um dies nicht einzelnen Produkten oder Architekturen zuordnen zu können – das ganze ist eher als Grundlagen-Arbeit und kaum als konkretes Chip-Projekt zu verstehen. Dabei hat AMD nicht einfach nur mehrere Chiplets auf ein Blatt Papier gemalt, sondern sich explizit der Frage gewidmet, wie man die Skalierung der Rechenleistung hoch halten bzw. die Datenströme zwischen den Chiplets reglementieren kann. Hierfür verbindet man mittels "High Bandwidth Crosslink" die Level3-Caches aller Chiplets, jene Anbindung wird über AMDs Interposer-Technologie (und damit vergleichsweise stromsparend) realisiert.

Als weiterer Clou arbeitet eines der Chiplets als "Master" ("Primary Chiplet"), die anderen dann als "Slave" ("Secondary Chiplet"), unabhängig deren Anzahl. Damit werden Betriebssystem wie Software nur ein einziger Grafikchip vorgegaukelt, die Lastverteilung passiert also komplett Chip-intern und muß nicht mehr die Sorge der Anwendungs-Entwickler sein. Damit wird das größte Problem der bisherigen MultiChip-Technologien SLI & CrossFire umgangen, dass jene eben direkten Support seitens der Anwendungs-Seite benötigt haben. Natürlich entscheidet sich alles daran, wie effizient diese Lastverteilung letztlich arbeitet – das System aufzustellen ist das eine, die Performance in der Praxis das andere. In jedem Fall kann hiermit nicht die gleiche Recheneffizienz wie bei einem entsprechend größeren monolitischen Chip erreicht werden, zudem wird der Datentransport zwischen den Chiplets zusätzlichen Stromverbrauch erzeugen.

Effektiv ist diese Lösung primär dann, wenn ein entsprechender monolitischer Chip schlicht zu groß (oder zu teuer zu fertigen) werden würde. Hierbei spielen vor allem Belichtungslimits von Halbleiter-Produkten sowie der Effekt, dass die Fertigungsausbeute bei größeren Chips deutlich abnimmt, mit hinein. Trotz größerem Technik-Einsatz und einer zusätzlichen Ineffizienz ist es in der Endabrechnung wohl günstiger, vier Chiplets à 200mm² anstatt eines großen Chips à 750mm² herzustellen. Normalerweise würde man angesichts dieser Ausgangslage somit eher in die Richtung gehen, primär professionelle Beschleuniger bzw. HPC/Compute-Produkte auf MultiChip-Basis aufzulegen – sprich in Richtung von AMDs CDNA-Serie. Der Punkt der Master/Slave-Unterteilung ist allerdings etwas, was eigentlich nur im Gaming-Bereich wichtig ist – denn im HPC/Compute-Bereich kommen die Anwendungen üblicherweise mit mehreren Beschleunigern im System problemlos zurecht, benötigen diesen Kunstgriff (zugunsten einer hohen Recheneffizienz) nicht.

Natürlich dürften professionelle Beschleuniger dennoch die ersten sein, welche von einem solchen MultiChip-Ansatz im GPU-Bereich profitieren. Die technologische Grundlage ist jedoch augenscheinlich darauf ausgerichtet, auch für Gaming-Lösungen nutzbar zu sein. Wie schnell AMD dies in real greifbare Produkt überführt, steht allerdings noch in den Sternen. Zum "Navi 31" Chip der RDNA3-Architektur wurde zwar schon ein MultiChip-Ansatz genannt, dies stellte sich später jedoch rein als Auftrennung in ein Core-Chiplet und ein Cache/Interface-Chiplet heraus, was noch nicht wirklich in die Richtung der Verwendung vieler (Rechen-)Chiplets geht. Zudem werden viele solcherart Grundlagen-Arbeiten auch einfach gemacht, um selbige dann in der Schublade zu haben – ohne dass ein konkreter Plan zur Verwendung existiert. Auch zu RayTracing wurde schon viele Jahre hin- und herspekuliert – bis es dann mittels "Turing" im Jahr 2018 tatsächlich in Silizium gegossen wurde.

In jedem Fall läßt sich sagen, dass die mit jedem neuen Fertigungsverfahren steigenden Halbleiterkosten diesen Ansatz mit der Zeit immer attraktiver machen, das ganze eigentlich folgerichtig irgendwann passieren muß. Der eigentliche Treiber dieser Entwicklung liegt dann allerdings in der Kostenfrage für die Grafikchip-Entwickler: Man kann sowohl die teure Herstellung von Groß-Chips umgehen, als auch kleinere Grafikchips ganz einfach über eine geringere Anzahl an "Slave"-Chiplets kreiieren – ohne diese kleineren Grafikchips (wie bisher) als extra Chips auflegen zu müssen. Mehr Performance sollte man sich (im Gaming-Bereich) von diesem MultiChip-Ansatz jedoch besser nicht erwarten, denn in dieser Frage limitiert derzeit nicht die Chipfläche, sondern viel eher der maximale Stromverbrauch – wenn die aktuellen Spitzen-Grafikkarten schon bei (deutlich) über 300 Watt Realverbrauch stehen.

Nachtrag vom 7. Januar 2021

Anbei zwei weitere, detaillierte Darstellungsformen zu AMDs MultiChip-Ansatz im GPU-Bereich:

Nachtrag vom 6. April 2021

VideoCardz berichten über ein neues AMD-Patent ("Active Bridge Chiplet with integrated Cache", PDF), welches sich erneut um technologische Fortschritte bei zukünftigen MultiChip-Grafiklösungen kümmert. Hierbei wird der zum Jahreswechsel beschriebene MultiChip-Ansatz um einen nunmehr aktiven Interposer mit eigenem Cache erweitert. Bisherige Interposer-Lösungen beinhalteten immer nur die Verbindungen zwischen den einzelnen Chiplets und gelten somit als "passiv". Über die Hinzunahme eines eigenen Caches wird der Interposer hingegen als "aktiv" eingeordnet, was einen zusätzlichen Stromverbrauch sowie einen höheren Fertigungsaufwand bedeutet. Andererseits ist die Fläche schließlich sowieso da, das Package wird damit auch nicht größer – und in jedem Fall sind interne Caches immer nutzvoll zum Abfangen von Speicherzugriffen, dies hatte AMD erst kürzlich mit dem "Infinity Cache" der RDNA2-Architektur (erfolgreich) demonstriert.

Insofern ist ein aktiver Interposer mit eigenem Cache eine logische Weiterentwicklung der vorhandenen MultiChip-Ansätze bzw. war durchaus sogar derart erwartet worden. Die Anwendungsmöglichkeiten dürften sich nicht einmal nur auf den Grafikchip-Bereich beschränken, sondern genauso auch in den CPU-Bereich hineingehen – wo mehr Cache erstens (im Server-Bereich) immer gern gesehen wird und zweitens natürlich auch zugunsten der Effizienz von MultiChip-Lösungen arbeitet. Am Schema-Aufbau ändert sich dabei eigentlich gar nicht so viel, man kann sich den "High Bandwith Crosslink" einfach nur noch mit einem großen Cache verbunden vorstellen, welcher dann um die Chiplets herum auf dem Interposer verteilt wird. Einzig die Bezeichnungen würden somit wechseln: Der Interposer-Cache würde zum "Last Level Cache", der Cache in den Chiplets selber würde wiederum zum Level3- oder Level4-Cache (je nach angesetzter Cache-Struktur).

Verwandte News

- Erste Tests geben AMDs temporalem Upscaler "FSR 2.0" gute Wertungen

- nVidia bringt mit "nVidia Image Scaling" einen eigenen offenen Upscaler in Konkurrenz zu AMDs FSR

- Neuer Artikel: Ein erster Überblick zur RayTracing-Performance

- Umfrage-Auswertung: Wie häufig werden VSR/DSR/Downsampling Anti-Aliasing genutzt?

- Erste Testberichte zu AMDs "FidelityFX Super Resolution" zeigen Stärken & Schwächen des DLSS-Kontrahenten

- Microsoft bringt das DirectX Feature-Level 12_2 mit verpflichtendem Support von RayTracing und Shader Model 6.5

- Microsoft stellt "DirectX 12 Ultimate" mit vier verpflichtenden "neuen" Grafik-Features vor

- Umfrage-Auswertung: Wie weit verbreitet ist Multi-GPU im Jahr 2019 noch?

- Umfrage-Auswertung: G-Sync vs. FreeSync - was ist bereits im Einsatz, was zieht mehr Interesse an (2019)?

- AMD gibt Ausblick auf die RDNA2-Architektur und RayTracing mit AMD-Grafikchips