Hauptlinks

Suchen

Hardware- und Nachrichten-Links des 15. Juni 2017

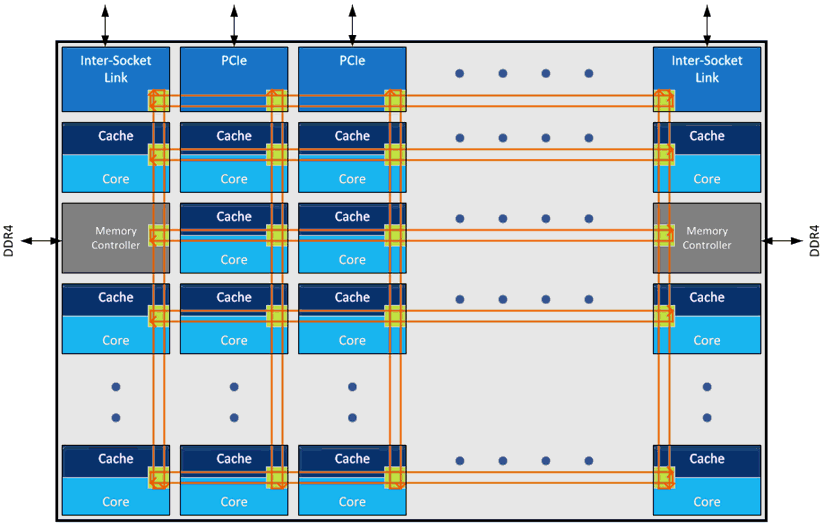

Gestern wurde an dieser Stelle noch über Bedenken berichtet, Intel könnte im anstehenden Zweikampf zwischen Core X vs. Threadripper mit seinem Ringbus etwas ins Hintertreffen geraten (besonders bei vielen CPU-Kernen) – heute nun kommt seitens Heise die Meldung, wonach Intel ausgerechnet bei Skylake-SP (den Server-Varianten von Skylake und damit der technischen Grundlage von Skylake-X) den Ringbus zugunsten eines Mesh-Konzepts ersetzt hat. Mittels einer solchen Netzwerk-artigen Verbindung will man die Skalierung bei besonders vielen CPU-Kernen hochhalten, hinzu kommen sogar noch positive Effekte beim Stromverbrauch. Dies eröffnet die Rechnung natürlich gänzlich neu, denn damit kann man bei Skylake-X jeglich Analogien zu früheren Server/Enthusiasten-Prozessoren von Intel vergessen, ein einfaches Hochrechnen mit ein paar Prozentpunkten mehr IPC sowie höheren Taktraten führt damit nicht mehr zum Ziel. Um so interessanter wird es dann natürlich, wie dieser Wettstreit der Vielkern-Prozessoren ausgeht – jeder der beiden Anbieter hat da wohl seine Chance, das Ganze wird nunmehr eher denn zum offenen Rennen.

Interessanterweise spricht man bei Heise auch davon, das das früher schon gezeigte MCC-Die von Skylake-SP zwei "Spezialkerne" anstelle echter CPU-Kerne enthalten soll, welche die Speichercontroller des Prozessors enthalten – dies entspricht auch einem von Intel offiziell freigegebenen Blockschaltbild. Dies bedeutet letztlich, daß das MCC-Die von Skylake-SP nur 18 CPU-Kerne (und nicht 20) enthält – was hier und da schon so angenommen wurde, aber bislang einfach noch unsicher war. Gleichfalls ist es damit wahrscheinlich, daß das LCC-Die von Skylake-SP nicht gleich 12, sondern nur 10 CPU-Kerne aufweist, genauso wie das HCC-Die von Skylake-SP nur 28 und nicht gleich 30 CPU-Kerne aufweist. Der Core i9-7900X entspräche dann dem Vollausbau des LCC-Dies von Skylake-SP, der Core i9-7980XE dem Vollausbau des MCC-Dies von Skylake-SP. Auch die Frage nach der Anzahl der verbauten Speichercontroller bei den einzelnen Dies läßt sich nunmehr halbwegs sicher beantworten: MCC- und HCC-Die haben beide sicher ein 6-Kanal-Speicherinterface. Beim LCC-Die ist dies noch ein wenig ungewiß, angesichts der geringeren Anzahl an CPU-Kernen ist hier der Verbau eines 4-Kanal-Speicherinterface nicht unwahrscheinlich. Im Consumer-Segment wird das vorgenannte 6-Kanal-Speicherinterface allerdings sowieso nicht erscheinen (würde abweichende Mainboards erfordern).

| Die-Size | max. Cores | Speicherinterface | Consumer-Einsatz | |

|---|---|---|---|---|

| AMD Epyc | 4x ~200mm² | 32 | 8Ch. DDR4 | nicht geplant |

| Intel Skylake-SP HCC | ? | 28 | 6Ch. DDR4 | nicht geplant |

| Intel Skylake-SP MCC | ? | 18 | 6Ch. DDR4 | Core i9-7920X, -7940X, -7960X, -7980XE |

| AMD Ryzen Threadripper | 2x ~200mm² | 16 | 4Ch. DDR4 | Ryzen Threadripper |

| Intel Skylake-SP LCC | ~310mm² | wahrschl. 10 | 4Ch. DDR4 | Core i7-7800X, -7820X, Core i9-7900X |

| AMD Ryzen 3/5/7 | ~200mm² | 8 | 2Ch. DDR4 | Ryzen 3 1200 bis Ryzen 7 1700X |

| Intel Kaby Lake (-X) | 122mm² | 4 | 2Ch. DDR4 | Core i5-7400 bis Core i7-7740K |

Videocardz bieten die kompletten Spezifikationen nebst zugehöriger offizieller SPECint-Benchmarks aus AMDs Pressedeck zu den am 20. Juni antretenden AMD Epyc 7xxx Server-Prozessoren an – welche zumindest in technologischer Nähe zu den Threadripper-Prozessoren für das Consumer-Segment stehen. Allerdings setzt AMD bei allen seinen Epyc-Modellen tatsächlich das große 32-Core-Package ein, damit ein 8-Kanal-Speicherinterface und 128 PCI Express Lanes garantiert werden können – auch bei Epyc-Modellen mit nur 8 oder 16 freigeschalteten CPU-Kernen. Threadripper wird wie bekannt jedoch auf einem 16-Core-Package basieren und kann daher immer noch leicht abweichende Eigenschaften bei seinen Taktraten und den dafür benötigten TDPs aufweisen (da Threadripper damit maximal ein 4-Kanal-Speicherinterface samt 64 PCI Express Lanes aufbietet). Denn die Epyc-Taktraten sind eher denn handzahm zu nennen – eine typische Taktrate lautet hier auf 2.0 GHz Basetakt mit 3.0 GHz (maximalem) Turbotakt zu einer TDP von immerhin 170 Watt.

Hierbei wäre allerdings der Strombedarf der sehr breit aufgestellten Peripherie zu berücksichtigen – sowohl zur Verbindung der gleich 4 verbauten Dies auf dem Package als auch für das superbreite Speicherinterface und die riesige Menge an PCI-Express-Lanes. Teilweise ist AMD bei diesen Server-Modellen aber auch einfach ehrlicher bei der TDP als bei Ryzen 5/7, wo insbesondere die Topmodelle dann doch beachtbar mehr gezogen haben als gemäß der offiziellen TDP-Angaben zulässig gewesen wären. Am Ende läßt sich auf Basis dieser Daten zu den Epyc-Prozessoren auch nur recht wenig zu den Taktraten der Threadripper-Prozessoren vorhersagen – noch dazu, wo bei jenen handfeste Hinweise auf Basetaktraten von 3.2 bis 3.4 GHz sowie Turbotaktraten von (bis zu) 3.8 GHz bereits vorliegen. Allenfalls kann man mitnehmen, das AMD mit den Epyc-Prozessoren und gemäß deren SPECint-Benchmarks vor einem wirklich starken Wiedereintritt in den Server-Markt steht – in welchem vor gut einer Dekade die seinerzeitigen Opteron-Prozessoren schon einmal einen durchaus guten Ruf hatten (und natürlich auch gut zu AMDs Finanzergebnis beitrugen).