Hauptlinks

Suchen

Weiter rasant steigende Kosten für Chipfertigung und Fertigungsanlagen bis hin zum 2nm-Node

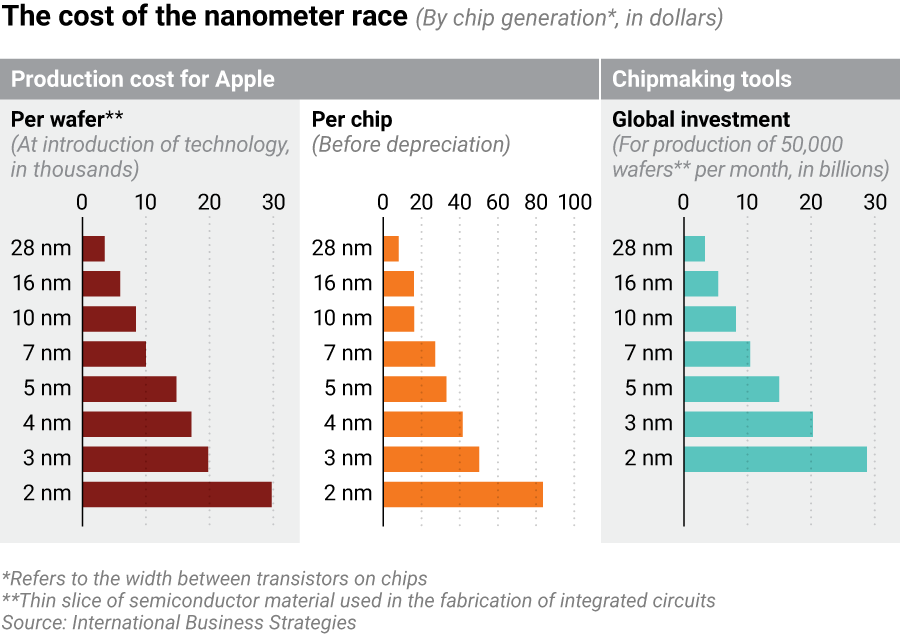

Ein sehr umfangreicher Artikel seitens Nikkei Asia, welcher eigentlich Chinas Aufholjagd im Bereich der Halbleiterfertigung betrachtet, bietet auch interessante Folien & Diagramme zum Fortschritt der einzelnen wichtigen Halbleiterfertiger wie auch zur bisherigen wie voraussichtlichen Kosten-Explosion bei immer kleineren Chip-Strukturen. Insbesondere letzteres ist interessant, denn hiermit wird für die 2nm-Fertigung ein enormer Kostensprung sowohl bei der reinen Chipfertigung als auch bezüglich entsprechender Chipwerke vorhergesagt. So sollen zwischen 3nm und 2nm die Wafer-Kosten um +51% steigen (berechnet für Apple, zum Start des jeweiligen Nodes), während die Fertigungsanlagen-Kosten um auch noch +42% zunehmen sollen. Dies wäre ein ähnlich teurer erkaufter Fortschritt wie zwischen 7nm und 5m (28nm zu 16nm ist schlecht vergleichbar, da hierbei der 20nm-Node ausgelassen wurde).

Die Problematik besteht auf beiden Seiten darin, dass die Absolut-Werte somit Höhen erreichen, welche für Consumer-Chips langsam aber sicher dem Bereich "ungangbar" nahekommen. So soll ein Apple-Soc der 2nm-Fertigung dann rein Chip-seitig über 80 Dollar kosten, mehr als 10mal so viel wie ein 28nm Apple-SoC (~8 Dollar). Normalerweise könnte sich Apple diese Kosten wohl leisten, aber natürlich soll an jedem iPhone auch mindestens die Hälfte des Verkaufspreises Brutto-Marge sein, da ist ein solch massiver Kostentreiber bei Apples Erbsenzählern sicherlich sehr unbeliebt. Ein typischer Gaming-Spitzenchip von nVidia mit angenommen 600mm² Chipfläche würde unter der 2nm-Fertigung bei angenommen 80% Yield im übrigen bei schlanken 410 Dollar Kostenpunkt herauskommen (der gleiche Chip unter der 28nm-Fertigung: $48).

Hinter dieser Preissteigerung steht aber natürlich auch ein Aufwand: Die Chipfertigungs-Anlagen für ein Halbleiterwerk mit einem Ausstoß von 50'000 Wafern pro Monat sollen unter der 2nm-Fertigung grobe 29 Milliarden Dollar kosten. Nur um dies in Relation zu setzen: TSMC hatte im dritten Quartal letzten Jahres in Vorbereitung der ersten 5nm-Chips von AMD und nVidia einen Wafer-Ausstoß von 150'000 5nm-Wafern pro Monat, somit die dreifache Menge. Um diese Wafer-Menge unter dem kommenden 2nm-Node in Chips umwandeln zu können, wären somit voraussichtlich Investitionen von ca. 90 Mrd. Dollar notwendig (reduziert sich sicherlich über Umrüstungen früherer Anlagen). Dies muß TSMC vorab auf den Tisch legen, ehe man seinen Abnehmern überhaupt den 2nm-Node anbieten und erst einige Quartale später (!) Einnahmen darüber erzielen kann.

| Wafer-Kosten | Fertigungsanlagen-Kosten | |||||

|---|---|---|---|---|---|---|

| Erklärung | berechnet für Apple, zum Start des jeweiligen Node | berechnet für 50'000 Wafer per Monat | ||||

| 28nm | ~3470 $ | 100% | - | ~3,2 Mrd. $ | 100% | - |

| 16nm | ~5840 $ | 168% | +68% | ~5,2 Mrd. $ | 163% | +63% |

| 10nm | ~8370 $ | 241% | +43% | ~8,1 Mrd. $ | 253% | +56% |

| 7nm | ~9950 $ | 287% | +19% | ~10,3 Mrd. $ | 322% | +27% |

| 5nm | ~14'680 $ | 423% | +48% | ~14,9 Mrd. $ | 466% | +45% |

| 4nm (Half-Node) | ~17'050 $ | 491% | - | - | - | - |

| 3nm | ~19'740 $ | 569% | +34% | ~20,3 Mrd. $ | 634% | +36% |

| 2nm | ~29'840 $ | 860% | +51% | ~28,9 Mrd. $ | 903% | +42% |

| Pixel-genaue Ableitung der Info-Grafik seitens IBS (weggelassen: Chip-Kosten, da augenscheinlich auf Apple-Chips und deren konkrete Chipfläche bezogen) | ||||||

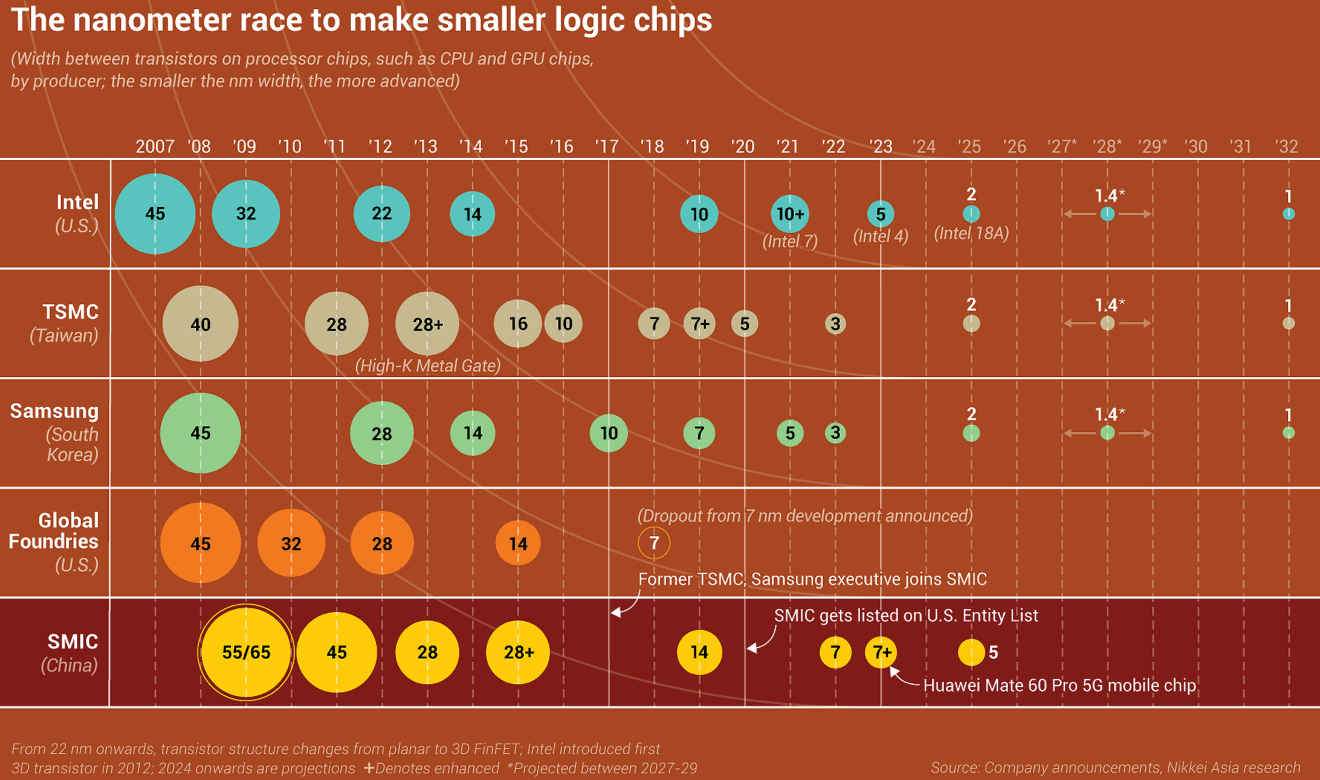

Auf diesem Punkt liegt auch das eigentliche Augenmerk jenes Artikels seitens Nikkei Asia: Danach geht man davon aus, dass die gewaltigen Investitions-Summen sowie die hohen Wafer-Kosten zukünftiger Fertigungsverfahren es den chinesischen Chipfertigern ermöglichen werden, die technologische Differenz zu Intel, TSMC & Samsung sogar besser zu überwinden. Dies passiert dann nicht dadurch, dass speziell SMIC besonders schnell neue Fertigungsverfahren bringt, sondern dass Intel, TSMC & Samsung einfach ihr bisheriges Tempo (angesichts dieser finanziellen Rahmenbedingungen) nicht mehr halten können. So geht man beispielsweise davon aus, dass Marktführer TSMC neue Fullnodes nicht mehr aller 2 Jahre, sondern zukünftig nur noch aller 3 Jahre herausbringen wird. Ein anderer Weg für China, schneller den Anschluß zu finden, soll im "Advanced Packaging" liegen, sprich der Stappelung mehrerer Chips – da hierbei die Grundtechnologien weit weniger anspruchsvoll sind und auch keine US-Sanktionen gelten.

Inwiefern dies den chinesischen Chipfertigern, allen voran SMIC, tatsächlich hilft, ist aber nicht wirklich gesagt. Insbesondere geht der Artikel sowieso von der nicht ganz korrekten Grundannahme aus, SMIC würde derzeit nur 1½ Node-Generationen hinter den westlichen Fertigern liegen. Korrekt wäre die Aussage "mindestens zwei glatte Fullnodes", zusammen mit der Einschränkung, dass SMICs 7nm-Node wohl nur eine Verbesserung des vorher schon existierenden 10nm-Nodes darstellt. Die eigentlichen Probleme für SMIC lauern eher hinter dem nunmehr erreichten, denn für noch kleinere Strukturen (außerhalb einer weiteren Verbesserung des Vorhandenen) würde man Fertigungsanlagen benötigen, welche auf den US-Sanktionslisten stehen. Und beim Aufbau einer eigenen Fertigungsanlagen-Industrie steht China eher noch am Anfang, zumindest ist dort der Abstand zu Marktführer ASML nochmals viel größer.

Eine weitere Chance für China, näher an die westliche Chipfertigung heranzurücken, ist mit einem anderen, im Artikel nur gestreiften Gedankengang zu sehen: Die hohen Waferkosten werden deren Abnehmer zunehmend dazu zwingen, immer mehr abzuwägen, welche neuen Chipprojekte tatsächlich die jeweils neueste Chipfertigung benötigen. Insbesondere im Consumer-Bereich haben die letztendlichen Produkte zumeist eine endliche Preisspirale, sprich deren Abgabepreis im Endverbraucher-Markt ist nicht beliebig zu erhöhen. Hier dürfte es in einiger Zeit anfangen, dass die Geräte-Hersteller wirtschaftliche Abwägungsentscheidungen treffen, welche mit der Zeit immer mehr Consumer-Chips hin zur zweitneuesten oder gar drittneuesten Fertigung wechseln lassen. Perspektivisch dürften bei der jeweils besten Fertigung am Ende nur noch diese Chips verbleiben, wo die Margen traditionell hoch sind – sprich Chips für professionelle Gerätschaften, somit für Server-/HPC- und AI-Anwendungen.

Bei Consumer-Chips wird man hingegen vermutlich in einiger Zeit sehen, dass die Hersteller anfangen, das jeweils beste Fertigungsverfahren auszulassen oder erst verspätet einzusetzen. Passiert dies, dann hätten die chinesischen Chipfertiger in der Tat eine gewisse Chance, sich bei den realen Produkten näher an die westlichen Chipfertiger heranzurobben – einfach weil man dann nicht mehr so weit springen muß wie bisher. Das Problem der Beschaffung von modernen Chipfertigungsanlagen besteht allerdings auch in diesem Fall, rein mit Verbesserungen des Vorhandenen wird man in China wohl nicht mehr wesentlich weiter kommen als bisher schon erreicht. Auch wenn der Artikel von Nikkei Asia sich eher hoffnungsvoll bezüglich der chinesischen Chipfertigung gibt, ist derzeit noch nicht einmal klar, wie allein der aktuelle Unterschied zwischen chinesicher und westlicher Chipfertigung überwunden werden kann – von NextGen-Nodes gar nicht erst zu reden.

Mitzunehmen aus westlicher Sicht ist aber vor allem der Punkt, dass in der mittelfristige Zukunft die Hersteller der wichtigen PC/Smartphone-Chips wohl überlegen werden, ob es wirklich in jedem Fall das neueste Fertigungsverfahren sein muß. Bei manchen Gerätschaften dürfte dies kaum einen Unterschied machen, da die Chips jetzt schon schnell genug sind, um alle Leistungsanforderungen zu erfüllen (Smartphone-SoCs). Bei anderen Gerätschaften wird der Entwicklungsfortschritt weiter ausgebremst werden, wenn ein Node-Wechsel vielleicht nur noch alle vier Jahre ansteht (CPUs & GPUs im PC-Bereich). Denkbarerweise dürfte es dann mehr Anstrengungen geben, auf Architektur-Ebene noch etwas herauszuholen. Bei manchen Chip-Projekten ist dies ein eher unterentwickelten Feld bzw. kann man sich derzeit einfach noch zu stark auf den obligatorischen Node-Sprung verlassen.

Alternativ dürfte auch die Nutzung von Zwischen-Nodes zunehmen: Sprich, es gibt Fertigungsfortschritt, aber anstatt einem vollen Nodesprung bewegt sich die Produktlinie immer nur um einen Half-Node vorwärts. Dies sieht optisch besser aus, garantiert ständige kleine Fortschritte – und führt dennoch insgesamt wieder zum Punkt, dass es einen neuen Full-Node nur noch aller vier Jahre gibt. So lange man keine Wege findet, die Kostenexplosion bei jedem neuen Fertigungsverfahren zu stoppen, wird dies allerdings für Consumer-Chips (aufgrund deren limitiertem Abgabepreis-Potential) gar nicht anders möglich sein. Wahrscheinlich ist auf Basis der aktuellen Chipfertigungs-Technologieschiene eine Kostenreduktion generell nicht mehr erreichbar, dies geht wohl nur bei gänzlich anderen Halbleiter-Technologien, welche derzeit bestenfalls Labor-Status haben. So lange da kein Durchbruch erfolgt, ist im Consumer-Bereich mit weiter stark steigenden Fertigungskosten und somit mittelfristig einem beachtbar langsameren Entwicklungstempo zu rechnen.

Nachtrag vom 24. Dezember 2023

Im Sinne der kürzlichen Ausführungen zu den rasant steigende Chipfertigungs-Kosten wäre sicherlich prophylaktisch zu überlegen, welche zukünftige Chip-Projekte von AMD, Intel & nVidia (des Consumer-Bereichs) hiervon betroffen sein könnten. Normalerweise sollte eigentlich alles, was in der Nähe von 1-2 Jahren liegt, sehr sicher hiervor sein, da die entsprechenden Chip-Projekte ihre Planungs-Phase bereits hinter sich haben und derzeit in der Ausführungs-Phase sind. Im gewissen Risiko sind somit "nur" Chip-Projekte, deren Marktstart eher auf 2025 oder später liegt, sprich zur 2nm-Generation gehören. Hier kommt dann auch der beschriebene, besonders hohe Kostensprung dieser Fertigung als Entscheidungs-Treiber hinzu, eventuell Consumer-Produkte von dieser Fertigung auszunehmen und nur Server/HPC/AI-Produkte in der neuen Fertigung aufzulegen.

| 5nm-Generation | 3nm-Generation | 2nm-Generation | |

|---|---|---|---|

| AMD CPUs | realisiert: Zen 4 | sicher: Zen 5 * | angenommen: Zen 6 |

| AMD GPUs | realisiert: RDNA3 | angeblich: RDNA4 | angenommen: RDNA5 |

| Intel CPUs | realisiert: Meteor Lake | sicher: Arrow Lake (20A) | sicher: Panther Lake (18A) |

| Intel GPUs | sicher: Battlemage | angenommen: Celestial | angenommen: Droid |

| nVidia GPUs | realisiert: Ada Lovelace | angeblich: Blackwell | angenommen: Rubin |

| * AMD nennt zur Fertigungs-Technologie von Zen 5 ganz offiziell "4nm | 3nm". Dies könnte durchaus bedeuten, dass einzelne Consumer-Produkte bereits hier im älteren Node antreten. | |||

Bei AMD sind somit im Risiko in jedem Fall Zen 6 und RDNA5. Gerade Zen 6 könnte diese Auftrennung nach Abnehmer-Segmenten ermöglichen, da AMD hierbei wohl verschieden große CCDs (8C, 16C, 32C) auflegen will. Auch bei nVidias Blackwell-Nachfolger Rubin könnte man derart handeln, nur die HPC-Lösungen unter der 2nm-Fertigung herzustellen und sich für die Consumer-Lösungen ein 3nm-Derivat herauszusuchen. Dies muß natürlich alles nicht passieren, neben Wirtschaftslichkeits-Erwägungen müssen die großen Chiphersteller immer auch sehen, was ihre jeweilige Konkurrenz macht und ob diese nicht Performance-mäßig in Vorhand geht, man ergo selber zum Nachziehen und somit zur modernern, teureren Chipfertigung gezwungen wird. Diese Entscheidung dürfte insbesondere bei den Nachfolgern der 2nm-Generation immer kritischer werden – und somit irgendwann auch einmal in Richtung "Wirtschaftlichkeit" ausfallen.

Es gilt somit in jedem Fall, zukünftig zu beobachten und vor allem die Unterscheidung zwischen Consumer- und Professional-Produkt herauszuarbeiten. Die Hersteller werden sicherlich anfänglich nicht geneigt sein, einen schwachen oder gar nicht vorhandenen Node-Fortschritt zuzugeben, sondern dies vielmehr versuchen zu maskieren. Dann kommt eben die Architektur "XYZ" unter "bis zu 2nm" – was alle Möglichkeiten offenläßt und im schlimsten Fall bedeutet, dass nur die HPC-Lösungen dieser Architektur unter der 2nm-Fertigung antreten, die Consumer-Lösungen dieser Architektur jedoch unter einem älteren Node. Insbesondere in Fällen, wo der Architektur/Generations-Name für Consumer- und HPC-Produkte gleichermaßen verwendet wird, besteht dieses Risiko (zutreffend bei: AMD-Prozessoren & nVidia-Grafikchips).

Verwandte News

- "Moore's Law" ist nur noch teilweise zu halten

- TSMCs 3nm-Fertigung wird (erneut) keine Performance-Verdopplung ermöglichen

- USA versuchen Chip-Lieferungen an Huawei per neuer Export-Beschränkungen zu unterbinden

- Simpler Grund der 14nm-Probleme: Intel muß wegen des Wettbewerbs mit AMD nunmehr viel größere Chips anbieten

- Die Flächen-normierten Fertigungskosten steigen nach dem 14/16nm-Prozeß um +30% pro Node

- Intel bringt mit der "Foveros" Technologie seinen eigenen Chiplet-Ansatz

- Der 7nm-Prozeß verdoppelt die Fertigungskosten (auf gleicher Chipfläche)

- Umfrage-Auswertung: Wann werden die ersten 7nm-basierten Gamer-Grafikkarten erwartet?

- GlobalFoundries stoppt die 7nm-Fertigung

- TSMCs 5nm-Fertigung bringt nur unterdurchschnittliche Fortschritte