Erster Überblick zur 5nm Grafikchip-Generation

Hauptlinks

Suchen

Erster Überblick zur 5nm Grafikchip-Generation (Seite 2)

Nachtrag vom 28. Juli 2021

Kepler_L2 @ Twitter macht mit einem Statement noch einmal ganz klar, was GCD und MCD unter der RDNA3-Architektur bzw. den MCM-Chips Navi 31 & 32 enthalten: Der GCD enthält den kompletten Grafikchip inklusive auch der Interfaces, allein der Infinity Cache fehlt – jener ist ausgelagert in den MCD. Die vorherigen, spekulativen Deutungen zum MCD haben meist eine höhere Funktionalität vermutet, nun aber handelt es sich hierbei schlicht nur um den (ausgelagerten) Infinity Cache – womöglich hergestellt in mehreren Slices wie beim kommenden 3D V-Cache der Zen-3-Prozessoren. Erst mit zukünftigen Chip-Generationen (Navi 41, RDNA4) könnte dann die Heraustrennung des I/O-Parts aus dem GCD erfolgen. Zudem wird "Graphics Core Die" als ausgeschriebener Name eines GCDs genannt (bisher spekulativ auch im Gespräch "Graphics Complex Die"), wobei leider der ausgeschriebene Name eines MCDs nicht erwähnt wird (spekulativ "Multi Cache Die" oder eher "Memory Core Die").

It's "Graphics Core Die" not complex actually. For MI200 the GCD contains everything (Naples-like design), for Navi31 it contains everything except the IC, for Navi41 and MI300 I imagine they will move more of the I/O to another die.

Quelle: Kepler_L2 @ Twitter am 28. Juli 2021

VideoCardz weisen auf einen Unterpunkt zu AMDs neuen Quartalszahlen hin, wonach AMD im zweiten Quartal 2021 bereits erste Auslieferungen zu "Radeon Instinct" HPC-Beschleunigern auf Basis der CDNA2-Architektur vermeldet hat. Damit dürfte dann nichts anderes als "Radeon Instict MI200" auf Basis des "Aldebaran"-Chips gemeint sein – und damit dem ersten MCM-Konstrukt beider Grafikchip-Entwickler. Selbiges war zwar generell etwas früher dran als die anderen 5nm-Projekte, wurde jedoch bislang eher nicht vor Jahresende 2021 erwartet. Mit diesen Auslieferungen muß der Tape-Out von Aldebaran schon einigermaßen zurückliegen, vermutlich Richtung Frühjahr 2020. Ob AMD hierfür wirklich schon den 5nm-Node von TSMC angesetzt hat, oder nicht doch vielleicht den (früher verfügbaren) 6nm-Node, wäre noch zu klären. In jedem Fall wurde die Termin-Tabelle im Artikel zur 5nm Grafikchip-Generation somit entsprechend aktualisiert.

Nachtrag vom 29. Juli 2021

In der Frage, mit was für einem Stromverbrauch die 5nm Grafikchip-Generation einhergehen wird, hat Kopite7kimi @ Twitter den kleinen Hinweis gegeben, dass man die GeForce RTX 40 nicht unterhalb 400 Watt ansetzen darf. Dies wird natürlich nur für das Top-Modell der jeweiligen Grafikkarten-Generation gelten – wobei sich die kleineren Modelle allerdings daran ausrichten werden und ebenfalls entsprechend jeweils höhere Stromverbrauchs-Werte auf die Waage bringen sollten. Wie hoch es für das Top-Modell über diese 400 Watt letztlich hinausgeht, ist unklar – aber nVidia sollte es normalerweise mit einer einzelnen Generation nicht übertreiben und daher die Watt-Steigerung pro Generation in einem überschaubaren Rahmen halten. Denkbar ist also irgendetwas bei 420-450 Watt – alles darüberliegende hat entsprechend geringere Chancen.

400 is not enough

Quelle: Kopite7kimi @ Twitter am 29. Juli 2021

Gänzlich verwunderlich kommt dies nicht, denn die Grafikchip-Entwickler kämpfen hier gegen zwei Effekte: Zum einen sind die Fortschritte in der Halbleiterfertigung perspektivisch nicht darauf ausgerichtet, einen dem Flächengewinn ebenbürtigen Stromverbrauchs-Effekte zu erzielen. Nutzt man also den Flächengewinn (vollkommen) aus, dann ergibt sich immer ein etwas höherer Stromverbrauch – meistens sogar mit einer größeren Differenz, als was man durch Effizienz-Verbesserungen auf Architektur-Ebene wieder auffangen könnte. Und zum anderen gehen AMD & nVidia die 5nm-Generation wie bekannt mit heftigen Hardware-Sprüngen an – welche generell unmöglich zum selben Stromverbrauch abzuleisten sind. Nachdem nVidia mit der Ampere-Generation die viele Jahre lang bei nVidia geltende 250W-Grenze deutlich durchbrochen hat, ist nun augenscheinlich die Scheu vor höheren Watt-Zahlen gefallen – und man bringt somit das, was man Chip-technisch bestenfalls realisieren kann, unabhängig des daraus resultierenden Stromverbrauchs.

Dies dürfte dann wegen des erstgenannten, grundsätzlichen Effekts bei zukünftigen Chip-Generationen und Fertigungsverfahren nicht wesentlich anders laufen. Der harte Wettbewerb zwischen den Grafikchip-Entwicklern verhindert auch, dass man sich selber irgendwo begrenzt – das konnte sich nVidia nur zu den Zeiten leisten, wo man sich klar vor AMD wusste. Auch bei AMD darf man zukünftig somit eine vergleichsweise ähnliche Strategie erwarten – wobei der getroffene MultiChip-Ansatz mit der dreifachen Menge an FP32-Einheiten beim "Navi 31" Chip ja faktisch schon darauf hindeutet, dass es unmöglich ohne höheren Stromverbrauch gehen wird. Bondrewd im Beyond3D-Forum hat AMDs Zielsetzung mit "Navi 31" bereits sehr klar dargelegt: Navi 31 soll außerhalb der Reichweite anderer (normaler) Chip-Projekte antreten. Nicht umsonst soll nVidia laut Kopite7kimi über einen (nachgereichten) Navi-31-Konter in Form eines "GH202" Chips aus der Hopper-Generation nachdenken.

It's a config designed around being unreachable by anything or anyone.

Quelle: Bondrewd @ Beyond3D-Forum am 23. Juli 2021

Denn der Silizium-Einsatz von Navi 31 dürfte sich für die beiden GCDs von Navi 31 auf allein ca. 600-650mm² belaufen (laut Bondrewd ist ein GCD kleiner als 350mm²), hinzukommend das MCD (was wahrscheinlich schlicht aus mehreren Slices an 3D V-Cache besteht) kann man insgesamt von vielleicht 800mm² Chipfläche für Navi 31 ausgehen. Dies dürfte deutlich mehr sein als der AD102-Chip von nVidia, welcher vermutlich bei +71% mehr Shader-Clustern und dem erheblichen Sprung von Samsung 8nm auf TSMC 5nm vielleicht sogar etwas kleiner als der GA102-Chip (628mm²) herauskommt. Zur Wattage von Navi 31 gibt es noch nichts griffiges, laut Bondrewd sollen es jedoch keine 500 Watt werden. Irgendetwas im Rahmen von 450-480 Watt ist für Navi 31 jedoch durchaus vorstellbar, angesichts des Vergleichs zu AD102 sowie gerade der zu Navi 31 kolportierten Hardware-Daten.

| AMD Navi 31 | nVidia AD102 | |

|---|---|---|

| Chip | TSMC 5nm, MCM, insgesamt vermutlich ~800mm² (oder mehr) | TSMC 5nm, monolithisch, vermutlich ~600mm² |

| Hardware | 6 SE, 60 WGP, 15'360 FP32, Infinity Cache, 256 Bit GDDR6 | 12 RE, 144 SM, 18'432 FP32, 384 Bit GDDR6X |

| Stromverbrauch | vermutlich Richtung 450-480 Watt | vermutlich Richtung 420-450 Watt |

| Anmerkung: reine Wiedergabe von Gerüchten – keine offiziellen Daten | ||

Nachtrag vom 2. August 2021

Von Twitterer TtLexington kommt eine Serie an Tweets zur GeForce RTX 40 Serie bzw. natürlich primär auf deren Spitzen-Chip "AD102" bezogen. Der Twitterer ist bislang noch nicht in Erscheinung getreten, insofern muß die Qualität dessen Informationen erst noch eruiert werden. Nach eigenen Angabe handelt es sich um Mitglied des chinesischen Zhihu-Forums, welcher dort im September 2020 für eine vergleichsweise gut zutreffende Performance-Aussage zu AMDs Navi-21-Chip (mindestens 3080er Level, im besten Fall nahe der 3090) gesorgt hatte. Zugunsten der neueren Tweets zur GeForce RTX 40 Serie spricht auch, dass jene entweder halbwegs auf bekanntes Wissen passen oder aber direkt von anderen Leakern bestätigt werden: So spricht Greymon55 @ Twitter genauso von "hohen" Taktraten bei der Lovelace-Generation – was der "TtLexington"-Aussage von 2.2 bis 2.5 GHz gleich ein ganz anderes Gewicht verleiht.

RTX 40 series: 2.2g-2.5g boost

Quelle: TtLexington @ Twitter am 1. August 2021

rtx30series—rtx40series like Maxwell—Pascal

Quelle: TtLexington @ Twitter am 1. August 2021

2022 12or2023Q1

Quelle: TtLexington @ Twitter am 1. August 2021

TSMC ,not can be samsung

Quelle: TtLexington @ Twitter am 3. August 2021

Mittels der höheren Taktraten sollte sich nVidia bei der FP32-Power weiterhin von AMD absetzen, könnte allerdings dann tatsächlich bei einem höheren Stromverbrauch landen. Womöglich liegt hierin die Erklärung dafür, dass die Tendenz der Leaker zuletzt dahin ging, AD102 den höheren Stromverbrauch zuzusprechen als Navi 31 – trotz dass AMD mit deutlich höheren Silizium-Aufwand herangeht und auch "TtLexington" wiederum TSMC als Chipfertiger bei nVidias 5nm-Generation bestätigt, nicht Samsung. Genauso bestätigt wird der hohe damit erzielbare Performance-Sprung, welcher sinngemäß ähnlich kräftig wie zwischen nVidias Maxwell- und Pascal-Generation aussehen soll (GeForce GTX 980 Ti → GeForce GTX 1080 Ti: +73%). Genauso wie die bekannten, verläßlichen Quellen ist "TtLexington" dann arg zurückhaltend bei der Terminlage: AD102 ist demnach nicht vor Dezember 2022 zu sehen – oder sogar erst im ersten Quartal 2023. In dieser Frage scheint AMD etwas schneller zu sein, wo zumindest das vierte Quartal 2022 angepeilt wird, sogar das späte dritte Quartal 2022 noch nicht ganz unmöglich ist.

Laut Bondrewd @ Beyond3D-Forum soll der Navi-33-Chip als der drittgrößte Chip der kommenden RDNA3-Architektur einen Midrange-Ansatz verfolgen, sprich für die Preisklasse von 450 Dollar gedacht sein. Dafür gibt es dann allerdings auch weniger Speicher als bei Navi 22 – welcher in Form der Radeon RX 6700 XT seine 12 GB trägt. Dies erhärtet die (vorher schon hier und da genannte) These, wonach Navi 33 nur mit einem 128-Bit-Interface anrückt, dazu passen dann wirklich nur 8 (oder 16 GB) Speicher. Trotzdem würde es verwundern, wenn AMD in dieser Frage bei einer 450-Dollar-Karte knausrig wäre – dies ist dann immerhin schon Ende 2022 und muß voraussichtlich bis ins Jahr 2024 reichen. Andererseits sind Fragen der Speicherbestückung auch eine Angelegenheit der konkreten Kartengestaltung, welche man – wie zuletzt ausgeführt – eigentlich erst mit Vorliegen eines validierten Grafikchips angeht.

Ballpark ~440mm^2 but it's also less mem than N22.

Feasiable for 450 buck.

Quelle: Bondrewd @ Beyond3D-Forum am 28. Juli 2021

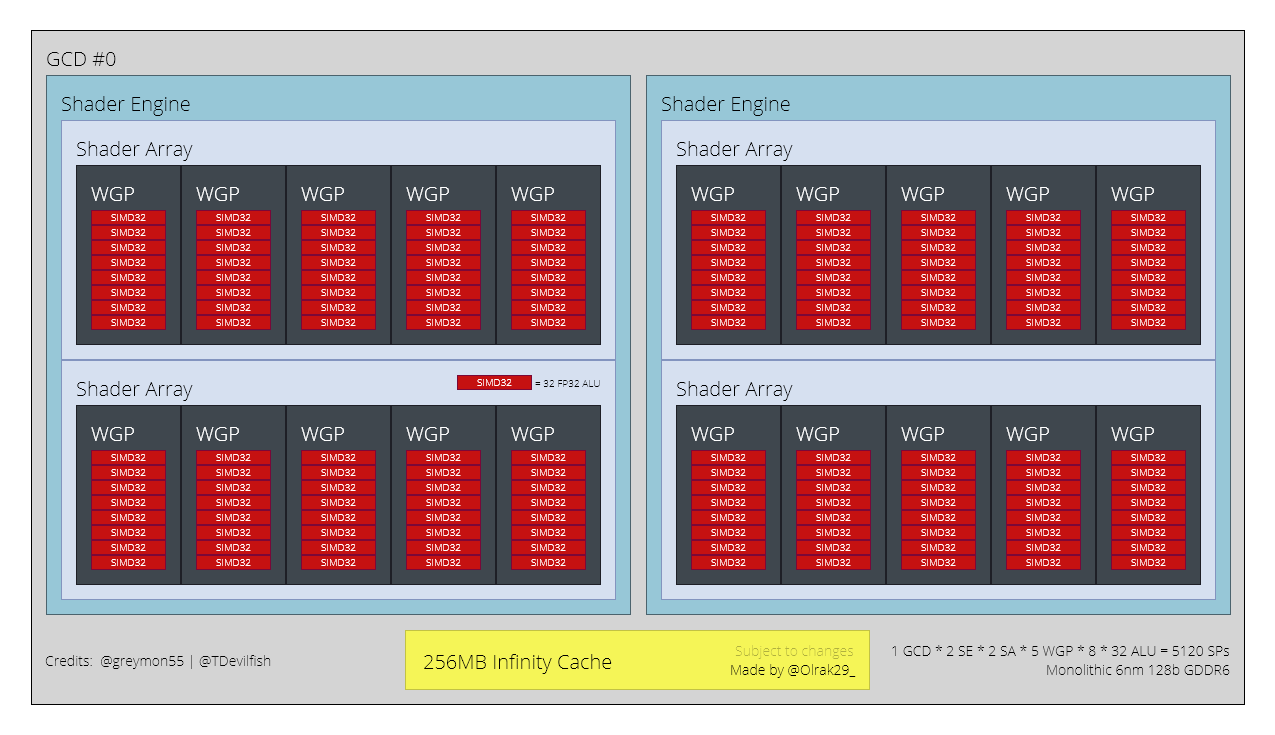

Interessant ist zudem die Notiz zur Chipgröße von Navi 33: Danach sollen es immerhin 440mm² sein. Dies erscheint gegenüber den 519mm² von Navi 21 als ziemlich kleiner Unterschied – erklärt sich allerdings wohl darin, dass die für Navi 33 (im Gegensatz zu Navi 31/32) angesetzte 6nm-Fertigung gegenüber 7nm nur einen Flächenvorteil von –16% erbringt. Navi 33 wird augenscheinlich dieselbe Anzahl an FP32-Einheiten wie Navi 21 mitbringen, zu allerdings einem halbierten Speicherinterface (256 Bit → 128 Bit) und jedoch voraussichtlich derselben Menge an Infinity Cache (128 MB). Unklar ist, wie stark dann die Architektur-Änderungen ins Transistoren-Budget sowie den Flächenbedarf einschlagen – aber angesichts dessen, dass AMD mit Navi 33 (angeblich) in Richtung der Performance von Navi 21 gehen will (und man zudem einigen Nachholbard beim Thema "RayTracing" hat), ist eine gewisse dickere Architektur eigentlich obligatorisch.

| Navi 33 | Navi 32 | Navi 31 | |

|---|---|---|---|

| Chips | monolithisch | 2 GCD + MCD | 2 GCD + MCD |

| Fertigung | 6nm TSMC | GCD: 5nm TSMC, MCD: 6nm TSMC | |

| Chipfläche | ~440mm² | unbekannt | geschätzt ~800mm² (oder mehr) |

| Hardware-Daten | 2 Shader-Engines 20 WGP mit 5'120 FP32 |

4 Shader-Engines wahrscheinlich: 40 WGP mit 10'240 FP32 |

6 Shader-Engines 60 WGP mit 15'360 FP32 |

| Speicherinterface | 128 Bit GDDR6 | unbekannt | 256 Bit GDDR6 |

| Infinity Cache | vermutlich 128 MB | unbekannt | vermutlich 512 MB |

| Perf-Ziel | Richtung Navi 21 | unbekannt | Navi 21 x2,5-2,7 |

| Tape-Out | Q4/2021 | unbekannt | in Bälde |

| Anmerkung: reine Wiedergabe von Gerüchten – keine offiziellen Daten | |||

Nochmals Bondrewd notiert hierzu beispielsweise, dass AMD bei der RNDA3-Architektur nicht den Weg von nVidia bei der Ampere-Architektur gegangen sein soll, wo nVidia die verdoppelten FP32-Einheiten mehrheitlich ohne entsprechend mehr Verwaltungslogik hingestellt hatte. AMD hat bei RDNA3 zwar die "Compute Units" (CU) zugunsten der WGPs abgelöst sowie die WGPs mit doppelter FP32-Anzahl aufgestockt, soll dazu aber (angeblich) auch insgesamt das ganze "Drumherum" entsprechend verbreitert haben. Damit könnte man dann einen größeren Performanceeffekt als nVidia bei deren FP32-Verdopplung generieren – was auch notwendig ist, denn ansonsten kommt Navi 33 niemals in die Nähe des Performance-Niveaus von Navi 21 (und wäre genauso die hohe Performance-Zielsetzung von Navi 31 außer Reichweite).

Instead of moar FP32 per same amount of regs they throw moar everything in a fat SM config.

Quelle: Bondrewd @ Beyond3D-Forum am 28. Juli 2021

Nachtrag vom 3. August 2021

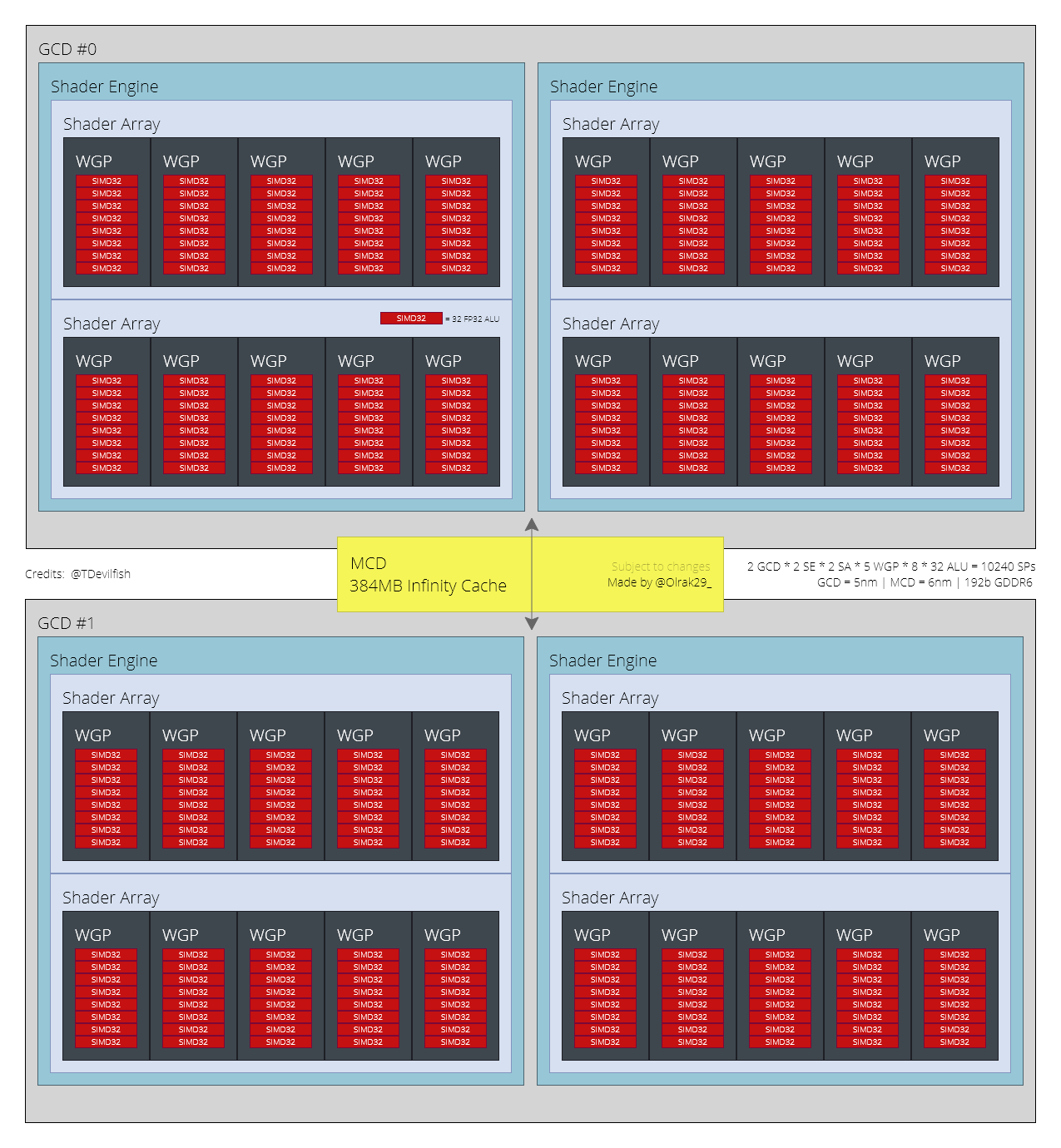

Twitterer 'Olrak29' (via VideoCardz in Form eines umfangreichen Postings zu Navi 3X) hat auf der Basis der bekannten wie vermuteten Daten zu den RDNA3-Grafikchips nun auch noch Blockdiagramme für Navi 32 sowie für Navi 33 angelegt – welche das kürzlich schon erstellte Blockdiagramm für Navi 31 ergänzen. Bei den groben Daten zu Navi 31 & 33 ist sich die Gerüchteküche derweil schon ziemlich sicher, vakant sind primär die Daten zu Navi 32 sowie jene zu Speicherinterface und Infinity Cache aller drei Navi-3X-Chips. Insbesondere dass zu Navi 33 kolportierte, nur 128 Bit breite Speicherinterface stößt breit auf Unglauben, da jenes als zu klein erscheint, um damit immerhin 5120 FP32-Einheiten (wie bei Navi 21) ausreichend mit Speicherbandbreite zu füttern.

Eine mögliche Erklärung hier gegenüber liefert allerdings der Effekt des Infinity Caches bzw. der jeweiligen Hit- und Missraten, wie jene bereits von Locuza im 3DCenter-Forum eindrücklich dargelegt wurden. Auf der gleichen Menge an Infinity Cache (128 MB) hat ein Navi-21-Chip eine "Cache Miss Rate" von 38% unter 4K zu beklagen – nur in diesen 38% der Fälle kommt dann das 256bittige Speicherinterface zum Einsatz. Setzt man den Navi-33-Chip mit 128 MB Infinity Cache auf eine FullHD-Aufgabe an, dann fällt dessen "Cache Miss Rate" auf 20%, was fast die Hälfte ist – womit auch ein halb so breites Speicherinterface (für FullHD) ausreichend wäre. Größere Cache-Mengen würden dann den Navi-33-Chip sogar zur sinnvollen Arbeit unter WQHD befähigen – wobei diese Cache-Menge nicht garantiert werden kann, mehr als 128 MB Infinity Cache bei Navi 33 sind derzeit unsicheres Terrain.

| Navi 33 | Navi 32 | Navi 31 | |

|---|---|---|---|

| Chips | monolithisch | 2 GCD + MCD | 2 GCD + MCD |

| Fertigung | 6nm TSMC | GCD: 5nm TSMC, MCD: 6nm TSMC | |

| Chipfläche | ~440mm² | unbekannt | geschätzt ~800mm² (oder mehr) |

| Hardware-Daten | 2 Shader-Engines 20 WGP mit 5'120 FP32 |

4 Shader-Engines wahrscheinlich: 40 WGP mit 10'240 FP32 |

6 Shader-Engines 60 WGP mit 15'360 FP32 |

| Speicherinterface | 128 Bit GDDR6 | vermutlich 192 Bit GDDR6 | 256 Bit GDDR6 |

| Infinity Cache | vermutlich 128-256 MB | vermutlich 384 MB | vermutlich 512 MB |

| Perf-Ziel | Richtung Navi 21 | unbekannt | Navi 21 x2,5-2,7 |

| Tape-Out | Q4/2021 | unbekannt | in Bälde |

| Anmerkung: reine Wiedergabe von Gerüchten – keine offiziellen Daten | |||