Erster Überblick zur 5nm Grafikchip-Generation

Hauptlinks

Suchen

Erster Überblick zur 5nm Grafikchip-Generation (Seite 3)

Nachtrag vom 5. August 2021

Twitterer TtLexington, welcher kürzlich mit Aussagen über die GeForce RTX 40 Serie in Erscheinung trat, hat nun auch noch eine sehr interessante Aussage zur Performance-Konstallation Navi 31 vs AD102 getroffen. Die hauptsächliche Aussage, wonach Navi 31 eventuell AD102 schlagen können soll, ist dabei weniger ungewöhnlich. Dies ergibt sich schon augenscheinlich anhand der herumgereichten Performance-Ziele von "Navi 31 = 2,5 x Navi 21" sowie "AD102 = 2,0 x GA102", wenn die aktuellen Grafikchips Navi 21 und GA102 letztlich in der Spitze als nur wenig unterschiedlich schnell angesehen werden. Viel interessanter ist eher die nachfolgende Aussage zur RayTracing-Performance von Navi 31 – welche sich nur indirekt mittels der Antwort auf die Behauptung eines anderen Twitterers ergibt:

but navi31 maybe beat ad102

Quelle: TtLexington @ Twitter am 1. August 2021

It will in raster.

Quelle: Talel Sghaier @ Twitter am 1. August 2021

ALL

Quelle: TtLexington @ Twitter am 2. August 2021

Denn hiermit wird faktisch versprochen, dass Navi 31 bzw. die RDNA3-Generation nicht mehr bei der RayTracing-Performance gegenüber AD102 bzw. der Lovelace-Generation zurückliegt. Da Navi 31 zwar vor AD102 herauskommen soll, der Abstand jedoch nicht wirklich groß ist, kann sich AMD somit bei der RayTracing-Performance der 5nm-Grafikchips keinerlei Abschläge gegenüber nVidia leisten. Anders formuliert: Unter RDNA3 muß die RayTracing-Performance in Relation der Rasterizer-Performance entsprechen – anders geht dieses Versprechen des Twitterers nicht auf. Es bleibt zu hoffen, dass sich dahinter ernsthafte Informationen zur Ausgestaltung bzw. Verbesserung der RayTracing-Performance unter der RDNA3-Architektur verbergen. Denn natürlich ist dies derzeit nicht mehr als ein Gerücht von noch in Überprüfung befindlicher Quelle, welches mit der nötigen Prise Salz genossen werden sollte.

Wirklich unmöglich ist das ganze allerdings auch nicht, denn eine gleichwertige RayTracing-Performance muß eigentlich die zwingende Zielsetzung von AMD für eine neue Grafikkarten-Generation für das Jahresende 2022 sein. Zu diesem Zeitpunkt dürfte die aktuelle Trennung der Benchmarks nach mit/ohne RayTracing zumindest für neue Grafikkarten aufhören, muß sich dann jede Hardware unter der bestmöglichen Grafik erweisen und gibt es keine Ausreden mehr. Die Frage ist nur, ob AMD hierbei auch das einkalkulieren kann, was nVidia bei der RayTracing-Performance der Lovelace-Generation oben drauf legen wied – ein Punkt, den AMD derzeit eigentlich nur erahnen kann, wozu aber noch einige Zeit kein gesichertes Wissen vorliegen wird. nVidia hat halt früher mit dem Thema "RayTracing" angefangen, womit man normalerweise die besseren Karten hat, die einmal erreichte Pole Position auch mit einer neuen Grafikkarten-Generation zu verteidigen.

Nachtrag vom 6. August 2021

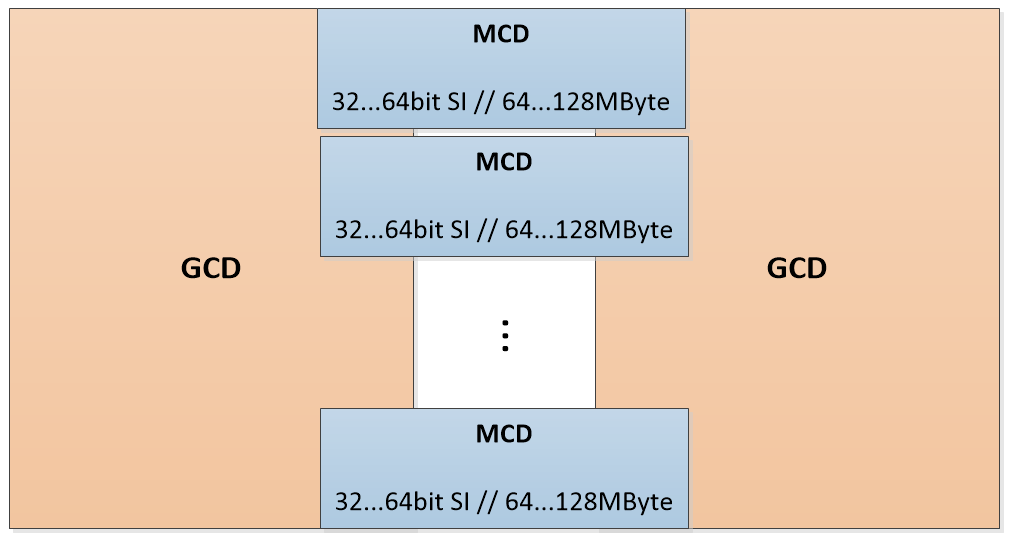

Bondrewd @ Beyond3D-Forum hat nochmals klarer gemacht, wie die MCDs in AMDs Multichip-Ansatz bei Navi 31/32 zu verstehen sind: Jene enthalten keine weitere Logik, sind auch kein Trägermaterial für Cache – sondern der Infinity Cache selber. Und dies dann in Chip-technisch mehrfacher Ausfertigung, sprich im eigentlichen sind es mehrere MCDs pro Grafikchip. Inwiefern AMD dann offiziell hierfür die Mehrzahl benutzt oder Marketing-technisch von nur "einem MCD" sprich, ist noch nicht heraus. Wie kleinteilig es wird, ist genauso bekannt – aber die Wortwahl seitens Bondrewd läßt wohl darauf schließen, dass es definitiv mehr als zwei Cache-Dies sind, wahrscheinlich eher in Richtung 4 oder 8 Cache-Dies (bei Navi 31 mit vermutlich 512 MB Infinity Cache).

MCDs are the cache dies.

Two GCD and fuckton of MCD.

Quelle: Bondrewd @ Beyond3D-Forum am 1. August 2021

Dabei kommt diesem MCD dann nicht nur die Rolle zu, den Infinity Cache aus den GCDs von Navi 31/32 herauszulösen – sondern wohl auch die Rolle des gemeinsamen Video-Speichers, wo also die von beiden GCDs erarbeiteten Teil-Bilder zusammengesetzt werden. Dies ergibt sich aus einer Aussage seitens Olrak29 @ Twitter, welcher damit primär die größere Menge an Infinity Cache bei Navi 31/32 begründet. Sofern diese These passt, macht die frühere Angabe, wonach Navi 33 zwar 128 MB Infinity Cache, Navi 32 & 33 jedoch 384 und 512 MB tragen sollen, sehr viel mehr Sinn – denn Navi 33 ist monolithisch und braucht daher den Inifinity Cache nicht zur Datenübertragung zwischen den beiden GCDs. Abschließend hierzu noch ein Nutzer-erstelltes Schema-Bild seitens basix aus dem 3DCenter-Forum: Zu beachten wäre allerdings, dass die MCDs laut der weiterführenden Diskussion eher denn unter den GCDs angebracht werden sollen.

Nachtrag vom 9. August 2021

In Ergänzung der News von letzten Freitag soll noch auf eine andere Auslegungsform zum MCD von Navi 31/32> hingewiesen werden, welche sich aus der Foren-Diskussion zur Meldung ergab: Danach kann man die zugrundeliegende Formulierung "fuckton of MCD" nicht nur in Richtung mehrerer Einzelchips auslegen – sondern auch in Richtung einer großen Cache-Menge auf allerdings einem Einzelchip. Die in der Freitags-News dargebrachte Auflösung eines MCD bestehend aus mehreren Einzelchips ist damit keineswegs so sicher, wie dort notiert wurde – beide Möglichkeiten existieren weiterhin. Natürlich würde eine Aufsplittung in Einzelchips aus der Sicht einer höheren Yield-Rate in der Chipfertigung besser kommen und entspricht auch sonst AMDs Tendenz, die Chips so kleinteilig wie möglich aufzuteilen – aber es sind halt auch andere Auslegungen denkbar und damit nicht vom Tisch.

MCDs are the cache dies.

Two GCD and fuckton of MCD.

Quelle: Bondrewd @ Beyond3D-Forum am 1. August 2021

Beispielsweise ergab sich aus der Foren-Diskussion ein interessanter Ansatzpunkt, wie man das GCD von Navi 31 doch noch für Navi 32 weiterverwenden könnte: Normalerweise gibt es für eine Salvage-Lösung keinerlei extra Chipnamen, sondern nur andere Chipversionen (Navi 31 XT, Navi 31 XL). Doch in diesem Fall könnte man eine Salvage-Lösung des Navi-31-GCDs mit einem eigenen, nur für Navi 32 verwendeten MCD kombinieren – und dann würde sich wiederum der extra Chipname "Navi 32" rechtfertigen, weil wenigstens zum Teil ein nirgendwo anders benutzter Chip (das N32-MCD) eingesetzt wird. Aus Sicht der Kostenlage erscheint diese These jedoch eher grenzwertig, denn damit würde man zwei GCDs um jeweils –33% beschneiden, nur um einen eigenen, etwas kleineren MCD einsetzen zu können. Den wenigsten Verschnitt hat nach wie vor die Auflösung von zwei unterschiedlichen GCDs bei Navi 31 & 32 sowie MCDs aus Einzelchips, womit die jeweiligen Spitzenlösungen gänzlich ohne deaktivierte Chipteile auskommen können.

An der grundsätzlichen Hardware-Power der drei Navi-3X-Chips ändern diese Diskussionen zur Auslegungen der Chip-Gestaltung im übrigen nichts – jene dienen eher dem besseren Verständnis, was AMD hierbei genau macht. Generell wird Navi 33 somit ein monolithischer Chip mit 5'120 FP32-Einheiten. Darüber gibt es dann nur noch Chiplets aus jeweils 2 GCDs und eben dem bewußten MCD. Dabei soll Navi 32 mit 10'240 FP32-Einheiten gegenüber Navi 33 die nominelle Hardware-Power glatt verdoppelt, während Navi 31 mit 15'360 FP32-Einheiten "nur" noch +50% auf Navi 32 oben drauf legt. Diese Aufteilung mag auf den ersten Blick wenig symetrisch aussehen, hat aber eventuell zwei Begründungen: Erstens könnten die MCM-Konstrukte nicht ganz so effektiv wie der monolithische Chip sein, womit man unter MCM-Bedingungen eventuell etwas mehr FP32-Einheiten für dieselbe Performance ansetzen muß.

| Navi 33 | Navi 32 | Navi 31 | |

|---|---|---|---|

| Bauform | monolithisch | 2 GCD + MCD | 2 GCD + MCD |

| FP32-Einheiten | 5'120 | 10'240 (+100%) | 15'360 (+50%) |

| Speicherinterface | 128 Bit | 192 Bit (+50%) | 256 Bit (+33%) |

| Infinity Cache | 128 MB | 384 MB (+200%) | 512 MB (+33%) |

| Anmerkung: reine Wiedergabe von Gerüchten – keine offiziellen Daten | |||

Und zweitens ist es sogar ziemlich üblich, bei den kleineren Chips im Portfolio glatte Hardware-Verdopplungen anzusetzen, den absoluten Spitzenchip dann hingegen mit geringerem Abstand zum zweitkleinsten Chip auszuführen. Ein perfektes Beispiel hierfür ist nVidias Maxwell-Serie, wo zwischen GM206 und GM204 eine Verdopplung der FP32-Einheiten vorliegt, der für Ti- und Titan-Karten verwendete GM200-Chip hingegen nur +50% mehr FP32-Einheiten gegenüber dem GM204 aufweist. Sicherlich könnte man dies auch anders (mehr symetrisch) gestalten, aber dann müsste entweder der Spitzenchip in technisch schwierig zu beherrschende Größenklassen gehen – oder halt der zweitbeste Chip deutlich kleiner werden, welcher jedoch oftmals wichtig ist für den Wettbewerb der Grafikchip-Entwickler untereinander. AMDs Aufteilung der Navi-3X-Chips macht so gesehen sehr viel Sinn: Navi 33 dürfte grob die Performance von Navi 21 bieten, Navi 32 bringt die Generations-typische Performance-Verdopplung – und Navi 33 setzt dem ganzen (Titan-mäßig) einen oben drauf.

Nachtrag vom 12. August 2021

Twitterer 'Greymon55' hat mit zwei Tweets – No.1 & No.2 – interessante Hinweise auf die Ausgestaltung der RDNA3-Generation unterhalb von Navi 33 gegeben. Denn hierfür wird AMD augenscheinlich keine RDNA3-basierten Grafikchips auflegen – selbige sollen mit Navi 33 enden. Damit würde sich zumindest erklären, wieso schon vergleichsweise viel zu Navi 31, 32 & 33 bekannt ist, jedoch kein Sterbenswörtchen zu Navi 34 & Co. Die nachfolgende Navi-4X-Generation (auf Basis der RDNA4-Architektur) soll dann hingegen mit höherer Anzahl an Grafikchips als Navi 3X antreten – sprich bei Navi 4X wird es dann wohl wieder explizite Mainstream- und Entry-Chips geben. Denkbar sogar, dass Navi 4X nochmals in der 5nm-Fertigung daherkommt – dann jedoch mit allen Chips unter 5nm und nicht einem Mix aus 5nm- und 6nm-Chips wie bei RDNA3.

Navi4x has more chip models than Navi3x.

Quelle: Greymon55 @ Twitter am 11. August 2021

Only N31-33 seems to be the RDNA3 core.

Quelle: Greymon55 @ Twitter am 11. August 2021

Wie AMD das Marktsegment unterhalb Navi 33 (angeblich im 450-Dollar-Bereich unterwegs) innerhalb der vermutlichen "Radeon RX 7000" Serie bestücken wird, ist dagegen derzeit offen bzw. liegt im Feld der Spekulationen. Eine hierzu oftmals angedachte Auflösung wäre die 6nm-Neuauflage von RDNA2-Grafikchips – folgend dem Trend, dass AMD die kleineren Chips dieser Grafikkarten-Generation wohl lieber in 6nm anstatt 5nm auflegt, wahrscheinlich um die zur Verfügung stehenden 5nm-Wafer anfänglich primär den eigenen Zen-4-Prozessoren zukommen zu lassen. Denkbar wäre an dieser Stelle aber auch die Weiterbenutzung der aktuellen 7nm-Technik, eventuell auch unter anderen Namen (aka "Rebrandings"). Ein Portfolio-Aufbau basierend auf Grafikchips unterschiedlicher Architektur- und Fertigungsstufen hat bei AMD durchaus Tradition – und damit spart man sich den einen oder anderen neu aufzulegenden Chip.

So oder so würde RDNA3 damit "nur" einen Aufsatz auf das RDNA2-Portfolio ergeben – Navi 21 würde durch Navi 33 ersetzt, oben drauf kommen dann Navi 32 & 31. Dies bedeutet primär, dass Radeon RX 6000 Grafikkarten basierend auf Navi 22/23/24 bestenfalls durch (somit nur leicht optimierte) 6nm-Varianten ersetzt werden, im schlechtesten Fall gibt es nur ein Rebranding innerhalb der Radeon RX 7000 Serie auf Basis desselben Chip-Unterbaus. Navi 22/23/24 bzw. eventuelle 6nm-Derivate davon dürften uns also vergleichsweise lange begleiten – bis weit in die 5nm-Generation hinein und damit über das Jahr 2022 hinaus. Augenscheinlich bringt erst die Radeon RX 8000 Serie auf Basis RDNA4 bzw. Navi 4X dann eine Ablösung dieser kleineren und mittleren RDNA2-Chips daher. Dies gilt natürlich nur, sofern sich dieses Gerücht, wonach es keine kleineren RDNA3-Chips unterhalb von Navi 33 gibt, letztlich halten läßt.

| Radeon RX 6000 | Radeon RX 7000 | |

|---|---|---|

| Navi 31 geschätzt $1000-1500, möglicherweise Radeon RX 7900 Serie |

||

| Navi 32 geschätzt $600-1000, möglicherweise Radeon RX 7800 Serie |

||

| Navi 21 $579-999, Radeon RX 6800/6900 Serien |

➔ | Navi 33 angeblich ~$450, möglicherweise Radeon RX 7700 Serie |

| Navi 22 $479, Radeon RX 6700 Serie |

➔ | Navi 22 (oder 6nm-Refresh von N22) geschätzt $350, möglicherweise Radeon RX 7600 Serie |

| Navi 23 $379, Radeon RX 6600 Serie |

➔ | Navi 23 (oder 6nm-Refresh von N23) geschätzt $250, möglicherweise Radeon RX 7500 Serie |

| Navi 24 geschätzt $200, möglicherweise Radeon RX 6500 Serie |

➔ | Navi 24 (oder 6nm-Refresh von N24) geschätzt $150, möglicherweise Radeon RX 7400 Serie |

| Anmerkung: rein spekulative Projektion, basierend auf Gerüchten & eigenen Annahmen | ||

Nachtrag vom 19. August 2021

Eine recht weite Verbreitung findet derzeit eine Aussage seitems Greymon55 @ Twitter, welche nur in Verbindung mit der vorherigen Frage seitens 3DCenter @ Twitter ;) zu verstehen ist. Dabei ging es um die letzte Woche skizzierte Aufstellung der Radeon RX 7000 Serie mit wahrscheinlich nur drei RDNA3-Chips – und dem Rest des Portfolios dann entweder bestehend aus Rebrandings der Radeon RX 6000 Serie oder bestenfalls 6nm-Refreshs der bekannten Navi-2X-Chips. Laut dem Twitterer sollen es die Option der 6nm-Refreshes sein – was in jedem Fall der bessere Weg gegenüber der Weiterbenutzung der vorhandenen Grafikchips wäre. Unter der 6nm-Fertigung kann man zwar keine Wunderdinge aus den vorhandenen RDNA2-Designs holen, dürfte sich aber wenigstens ausreichend von der Radeon RX 6000 Serie absetzen können, um nicht für Verstimmung bei Fachpresse und Grafikkarten-Käufern zu sorgen.

For the rest of the Radeon RX 7000 portfolio, AMD thus seems to have two options:

1) 6nm refreshes of Navi 24, 23, 22

2) further use of Navi 24, 23, 22, possibly with new card names

Quelle: 3DCenter @ Twitter am 16. August 2021

6nm refresh

Quelle: Greymon55 @ Twitter am 16. August 2021

Klar muß aber auch sein, dass dies ein derzeit ungelegtes Ei darstellt: Über die kleineren Grafikchips für die Radeon RX 7000 Serie ist einfach noch nichts handfestes bekannt, mehr als eine grobe Richtung läßt sich dazu noch nicht angeben. Sinn macht diese gleichzeitige Benutzung der 5nm- und 6nm-Fertigung sowie der Mix aus RDNA2- und RDNA3-Technik für AMD vor allem dann, wenn man die Forschungs- und Entwicklungsausgaben sparsam halten will (weniger neue Chips) und gleichzeitig die Kapazitäten der 5nm-Fertigung primär den eigenen Zen-4-Prozessoren zukommen lassen will. Im Sinne der aktuellen Ballung aller wichtigen AMD-Produkte auf allein der 7nm-Fertigung von TSMC ist dies kein verkehrter Gedanke – gerade da TSMC seine 7nm-Fertigung samt dem 6nm-Derivat nach der Einführung der 5nm-Fertigung natürlich nicht abrüsten wird, sondern jene noch viele Jahre mit großen Volumen aktiv bleiben wird. Darüber, dass die Mehrheit der NextGen-Grafikchips eben nicht aus der 5nm-Fertigung kommt, sondern vielmehr der 6nm-Fertigung, hofft AMD vermutlich eine Wiederholung der aktuellen Preis- und Liefersituation vermeiden zu können.

Nachtrag vom 16. September 2021

Von Twitterer Greymon55 kommt eine neue Wasserstandsmeldung zur Performance der Lovelace-basierten GeForce RTX 40 Serie – bezogen natürlich auf das jeweilige Spitzenmodell, nicht auf die komplette Serie. Hierfür dürften aktuelle Industrie-Gerüchte als Basis dienen – etwas anderes existiert derzeit mangels entsprechender Hardware sowie noch nicht. Danach wird eine Performance-Verdopplung gegenüber einer GeForce RTX 3090 durch eine kommende Lovelace-Spitzenlösung (auf AD102-Basis) als "konservativ" eingeschätzt – sprich, da soll dann noch Platz nach oben hin sein. Damit ist Faktor 2,0 eher als unterer Maßstab der Performance-Steigerung zu sehen, es könnte in der Realität dann auch leicht mehr werden – anzunehmenderweise vielleicht Faktor 2,2. Viel genauer läßt sich dies derzeit sowieso nicht sagen, da bei nVidia derzeit erst am reinen AD102-Chip gearbeitet wird, noch nicht an darauf basierenden Grafikkarten.

I think 2x 3090 is conservative.

Quelle: Greymon55 @ Twitter am 11. September 2021

So könnte auch eine GeForce RTX 4090 auf AD102-Basis diverse Abspeckungen aus Salvage-Gründen tragen, welche dann wiederum negativ in diese Rechnung eingehen – derzeit aber natürlich noch nicht abzusehen sind, die Arbeit an konkreten Grafikkarten wird erst nach (erfolgreichem) Tape-Out und Validierungsphase beginnen (grob Frühling/Mitte 2022). Allerdings muß nVidia bei Lovelace auch nicht zwingend dem Schema der bisherigen nVidia-Grafikkarten folgen und könnte die GeForce RTX 4090 durchaus noch näher an den Vollausbau des AD102-Chips heranbringen – einfach weil AMD zuletzt für den nVidia-Geschmack zu nahe herangekommen ist und nVidia somit vom Start weg alles einsetzen muß, was man an Hardware-Power zur Verfügung hat. Dass genannte Performance-Plus von (konservativ) +100% bedeutet aber auch, dass nVidia entweder/oder aus Architektur und Chiptakt noch so einiges herausholen muß, denn bezüglich der reinen Hardware wird AD102 "nur" +71% mehr FP32-Einheiten gegenüber dem aktuellen GA102-Chip mitbringen.

Andererseits wechselt nVidia für die Lovelace-Generation wie bekannt von Chipfertiger Samsung wieder zu Chipfertiger TSMC – womit nach der Taktraten-mäßig eher wenig (gegenüber der Turing-Generation) verbesserten Ampere-Generation somit ein kräftiger Taktraten-Sprung winken sollte. Interessant ist allerdings an dieser Stelle durchaus, dass sich bei Performance & Terminen die beiden NextGen-Designs von AMD und nVidia immer mehr anzunähern scheinen: Mit den ersten aufkommenden Gerüchten erschien AMDs RDNA3-Ansatz sowohl mächtiger als auch früher am Start. Der prognostizierte Performance-Vorteil für AMD ist nunmehr geschrumpft (allerdings noch vorhanden), bei der Terminlage ist es gemäß der letzten Gerüchte hingegen schon zu einem Gleichstand gekommen. Man will es nicht beschwören, aber dies folgt doch auffällig dem Schema von früheren AMD/nVidia-Generationen, wo AMD im frühen Gerüchte-Verlauf nahezu jedesmal deutlich höher eingeschätzt wurde, als was dann letztlich an realer Hardware-Power herausgekommen ist.

| AMD Navi 21 → Navi 31 | nVidia GA102 → AD102 | |

|---|---|---|

| Architektur | augenscheinlich deutlich veränderte Architektur (nicht nur wegen MCM), Wegfall der CUs (WGPs als neue hauptsächliche Ordnungseinheit), anscheinend 4 → 6 Shader-Engines, anscheinend 128 → 256 FP32 pro WGP | vermutlich vergleichweise ähnliche Grundarchitektur, 7 → 12 Raster-Engines (GPC), erwartbarer Taktraten-Sprung wegen Wechsels von Samsung auf TSMC |

| FP32-Recheneinheiten | 5'120 → 15'360 (+200%) | 10'752 → 18'432 (+71%) |

| (hochgerechnete) Rohpower | 21 TFlops → ~75-80 TFlops (+257-281%) | 36 TFlops → ~80 TFlops (+122%) |

| Performance-Target | 2,5 bis 2,7fache (+150-170%) | 2,0 bis ~2,2fache (+100-120%) |

| Terminlage | angeblich Oktober 2022 | angeblich Oktober 2022 |

| Anmerkung: reine Wiedergabe von Gerüchten – keine offiziellen Daten | ||

Nachtrag vom 17. September 2021

Ein weiterer Hinweis seitens Twitterer Greymon55 zur Ausgestaltung der kommenden GeForce RTX 40 Serie dreht sich um das Speicherinterface des größten Lovelace-Chips AD102 bzw. die daraus folgenden Speicherinterfaces für die Desktop-Grafikkarten GeForce RTX 4080 & 4090: Jene werden mit 320 bzw. 384 Bit angegeben. Beides dürfte zum jetzigen Stand eher nur Vermutungen des Twitteres sein, da die konkrete Produktplanung bei nVidia derzeit noch in der Konzeptionsphase stecken wird – zuerst muß schließlich der AD102-Grafikchip zum Tape-Out und von dort erfolgreich zurückkommen. Allerdings dürfte die maximale Hardware des AD102-Chips natürlich schon in Stein gemeißelt sein, da so kurz vor Tape-Out in diesen Fragen dann keine Änderungen mehr vorgenommen werden (würde zusätzlich an Zeit kosten und somit alle Terminpläne über den Haufen werfen).

4080 should be 320bit, 384bit on 4090.

Quelle: Greymon55 @ Twitter am 17. September 2021

Die eigentliche Information aus dieser Twitter-Aussage ist somit "nur" jene, dass auch der AD102-Chip wieder nur mit demselben Speicherinterface wie die letzten vorhergehenden Enthusiasten-Chips von nVidia antritt: 384 Bit. Dies ist keine ganz neue Information, sondern wurde schon vor einiger Zeit von gleicher Quelle derart berichtet (und zudem von anderen Quellen bestätigt). Interessant ist das ganze in Verbindung mit zwei anderen Punkten: Erstens einmal wird auch von AMDs RDNA3-Chips berichtet, dass jene nicht mit größeren Speicherinterfaces wie bisher antreten sollen (maximal 256 Bit). Und zweitens drängen neuere Spiele – wie derzeit "Deathloop" – nunmehr eigentlich zu größeren Speichermengen, gerade für neue Grafikkarten-Generationen zum Ende des Jahres 2022. An der Leistungsspitze stehen AMD & nVidia zwar auch derzeit schon vernünftig bis gut da, aber im Mittelbau hakt es insbesondere bei nVidia – die 8 GB Speicher, welche beim GA104-Chip verbaut werden, sind (spätestens) Ende 2022 einfach zu wenig.

Die einfache Möglichkeit würde in einer Speicherverdopplung bestehen – was allerdings den Nachteil hat, dass man jene auf das ganze Programm anwenden muß, damit nicht Mittelklasse-Modelle mehr Speicher als Spitzenmodelle bekommen. nVidia würde somit bei Speichermengen von 16 GB (AD104) und 20/24 GB (AD102) herauskommen, was technisch alle Speichermengen-Probleme lösen würde und zudem gute Verkaufsargumente ergibt. Für AMD ergäbe dies allerdings die Problematik, dass man dann von der Speichermenge her zurückliegen würde – während hingegen eine Verdopplung auf AMD-Seite zu teilweise absurd hohen Speichermengen bis 32 GB führt. Insbesondere für AMD würde es daher größeren Sinn ergeben, wenn 1,5-GByte-Speicherchips verfügbar wären – dann könnte man einen Mehrspeicher anbieten, müsste dafür jedoch nicht in Extreme gehen. nVidia hingegen dürfte bei einer glatten Speicherverdopplung gegenüber der aktuellen Generation am besten aufgehoben sein, allenfalls das absolute Spitzenprodukt bräuchte diese nicht wirklich.

| Speicherinterface | Vorgänger | 1,5-GB-Chips | Verdopplung | sinnvoll | |

|---|---|---|---|---|---|

| AMD Navi 31 | 256 Bit GDDR6 | 16 GB | 24 GB | 32 GB | sinnvoll: 24 GB |

| AMD Navi 32 | 192 Bit GDDR6 | 12 GB | 18 GB | 24 GB | sinnvoll: 18 GB |

| AMD Navi 33 | 128 Bit GDDR6 | 8 GB | 12 GB | 16 GB | sinnvoll: 12-16 GB |

| nVidia AD102 | 384 Bit GDDR6X | 12/24 GB | 18/36 GB | 24/48 GB | sinnvoll: 24 GB |

| nVidia AD104 | 256 Bit GDDR6X | 8 GB | 12 GB | 16 GB | sinnvoll: 16 GB |

| nVidia AD106 | 192 Bit GDDR6 | 6/12 GB | 9/18 GB | 12/24 GB | sinnvoll: 12 GB |

Nachtrag vom 24. Oktober 2021

Twitterer ExecutableFix packt die Hardware-Daten der "Radeon Instinct MI250X" aus. Die größte Lösung basierend auf AMDs "Aldebaran" HPC-Chip soll mit 110 Clustern pro Chiplet (bestätigt auf Nachfrage) zu Taktraten von 1.7 GHz mit 128 GB HBM2e-Speicher auf einer TDP von 500 Watt antreten. Interessanterweise basiert der Aldebaran-Chip weiterhin auf der 7nm-Fertigung, stellt also noch keinen Vorgriff auf die 5nm-Fertigung dar. Die theoretischen Rechenleistungen betragen gemäß 47,9 TFlops FP32 und FP64 sowie 383 TFlops FP16/BF16. Gegenüber dem vorhergehenden Arcturus-Chip gibt es also primär die Verdopplung der Cluster-Anzahl (in den realen Produkten nicht maximal ausgeführt) zuzüglich einer Fullrate-FP64-Power – und damit (dank höherer Taktrate) eine vierfache FP64-Performance. Wegen weiterhin der 7nm-Fertigung geht allerdings die TDP wie gesagt auf gleich 500 Watt hoch – wenngleich dies im HPC-Bereich weniger eine Rolle spielt, so lange nur die Performance stimmt.

| Vega | CDNA1 | CDNA2 | |

|---|---|---|---|

| Chip | Vega 20, 7nm TSMC | Arcturus, 7nm TSMC | Aldebaran, 7nm TSMC |

| HPC-Lösung | Radeon Instinct MI60 | Radeon Instinct MI100 | Radeon Instinct MI250X |

| Bauform | monolithisch | monolithisch | MCM (2 Chiplets) |

| Cluster (CU) | 64 | 120 (Chip: 128) | 2x 110 (pro Chiplet: 128) |

| Taktrate | 1800 MHz | ~1500 MHz | ~1700 MHz |

| FP16-Rechenleistung | 29,5 TFlops | 185 TFlops | 383 TFlops |

| FP32-Rechenleistung | 14,7 TFlops | 23,1 TFlops | 47,9 TFlops |

| FP64-Rechenleistung | 7,4 TFlops | 11,5 TFlops | 47,9 TFlops |

Wie beim Arcturus-Chip dürften auch Aldebaran einige elementare Teile eines Gaming-Grafikchips fehlen (denkbar: Rasterizer, TMUs, ROPs, Videoeinheit, Display-Kapazitäten), womit auch keine Zweitverwendung als Gaming-Grafikkarte möglich ist – im Gegensatz zu Vega 20, wo dies letztmalig bei AMDs HPC-Beschleunigern möglich war. In dieser Beziehung ist AMDs Auftrennung zwischen Gaming- und HPC-Bereich klarer als bei nVidia, wo innerhalb der Ampere-Generation HPC-Chips (GA100) sowie Gaming-Chips (GA10x) sogar noch unterhalb demselben Architektur-Namen laufen. Allerdings fehlen dem GA100-Chip zumindest die RayTracing-Einheiten der Gaming-Chips, womit man selbigen nicht wirklich für Gaming-Zwecke zweitverwenden könnte. Ein denkbarer Zweitnutzen für alle diese HPC-Chips besteht allerdings im Cryptomining – realisiert erst kürzlich mit der "CMP 170HX" auf GA100-Basis.