Hauptlinks

Suche

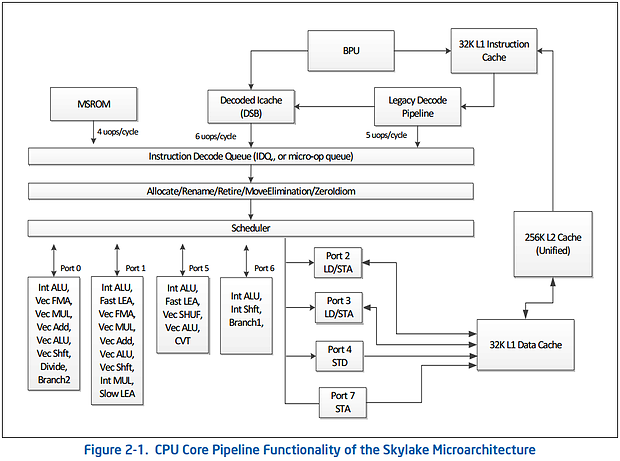

Blockschalt-Diagramm zu Intels Skylake-Architektur

Intel hat mittels eines eigentlich für Software-Entwickler gedachten PDFs erstmals genauere Details und sogar ein Blockschalt-Diagramm zur Skylake-Architektur herausgegeben. Bei dieser Gelegenheit fällt auf, daß Intel bis jetzt eben jene Architektur-Details immer noch nicht offiziell nachgeliefert hat, obwohl beim seinerzeitigen Skylake-Launch selbiges zeitnah versprochen wurde. Womöglich hat sich Intel auch deswegen so zurückgehalten, weil Skylake eher nur aus tief unter der Oberfläche liegenden Detailoptimierungen zu bestehen scheint, größere handfeste Änderungen sind Mangelware: Die Befehlsdekoder sind bei Skylake leistungsfähiger und spucken 5-6 MacroOps aus anstatt nur deren 4 – an der reinen Anzahl der Dekoder ändert sich jedoch gegenüber Haswell gar nichts.

| Sandy Bridge | Ivy Bridge | Haswell | Skylake | |

|---|---|---|---|---|

| Dekoder | 4 (4 MacroOps) | 4 (4 MacroOps) | 4 (4 MacroOps) | 4 (5-6 MacroOps) |

| Ports | 6 | 6 | 8 | 8 |

| ALUs | 3 | 3 | 4 | 4 |

| AGUs | 2 | 2 | 2 | 2 |

| FP | 2x 256 Bit | 2x 256 Bit | 2x 256 Bit | 2x 256 Bit |

| L1 Befehls-Cache | 32 kB, 8fach assoziativ | 32 kB, 8fach assoziativ | 32 kB, 8fach assoziativ | 32 kB, 8fach assoziativ |

| L1 Daten-Cache | 32 kB, 8fach assoziativ | 32 kB, 8fach assoziativ | 32 kB, 8fach assoziativ | 32 kB, 8fach assoziativ |

| L2-Cache | 256 kB, 8fach assoziativ | 256 kB, 8fach assoziativ | 256 kB, 8fach assoziativ | 256 kB, 4fach assoziativ |

Danach erschöpfen sich schon die wirklich notierbaren Änderungen, der Rest ist echte Detailarbeit. Intel hat gemäß Golem an der Geschwindigkeit der Caches gearbeitet, was zusammen mit dem leistungsfähigeren Dekoder für eine bessere Auslastung der Ausführungs-Pipeline sorgen dürfte – besonders interessant angesichts der mit der Haswell-Architektur eingeführten vierten ALU-Einheit, für welche es regulär eher schwer ist, noch Arbeit zu finden. Hinzu kommen noch ein paar neue Spezialeinheiten – welche allerdings eben auch nur in Spezialfällen wirklich eingesetzt werden.

In der Summe der Dinge hat Intel recht wenig am Haswell-Design herumoptimiert, sehen sich Haswell und Skylake doch sehr ähnlich. Damit ist man weit weg von früheren Intel-Standards, wo eine "neue CPU-Architektur" in aller Regel doch markante Änderungen mit sich brachte. Skylake ist jedoch eine sogar nur niedrige Optimierungsstufe von Haswell geworden, eine neue CPU-Architektur im Sinne des Wortes ist dies mitnichten (Punkte wie ein anderes Speicherinterface zählen hierbei nicht, da nicht den CPU-Kern betreffend). Die Architektur-Fortschritte bei Intel werden nun ganz augenscheinlich sehr klein – und dabei ist Skylake schließlich sogar schon der zweite Nachfolger von Haswell, dazwischen liegt regulär noch Broadwell. Die spannende sich hieraus ergebende Zukunftsfrage lautet: Ist Intel mit seinem Latein an Architektur-Optimierungen innerhalb der Core-Grundarchitektur nunmehr am Ende – oder hält sich bewußt zurück, um dann mit der Cannonlake-Architektur nach dem Release von AMDs Zen-Architektur alle Verbesserungen auf einen Schlag gebündelt zu bringen?

Verwandte News

- Intel bringt mit Cannonlake Achtkerner ins normale Consumer-Portfolio

- Intel stellt den (großen) Rest des Skylake-Portfolios offiziell vor

- Umfrage-Auswertung: Wie hoch läßt sich der Haswell-Refresh "Devils Canyon" in der Praxis übertakten?

- Umfrage-Auswertung: Wie ist der Ersteindruck zu Intels Skylake?

- Gesammelte Overclocking-Resultate zu Intels Broadwell

- Performance-Überblick Intel-Prozessorenarchitekturen von Core 2 zu Skylake

- Neuer Artikel: Launch-Analyse Intel Skylake

- Zweite Welle an Skylake Desktop-Prozessoren erscheint am 1. September

- Intel-Prozessoren Roadmap für die Jahre 2015-2018

- Weitere Benchmarks zum Core i7-6700K zeigen einen eher geringen Skylake-Vorteil