Hauptlinks

Suche

nVidia stellt den "GA100"-Chip der Ampere-Generation mit 8192 Shader-Einheiten an einem 6144 Bit HBM2-Interface vor

Mit einer Serie von 12 Videos hat nVidia seine für die abgesagte GTC im März angesetzte GTC-Keynote in Form der Vorstellung erster Ampere-basierter Produkte nachgeholt. Wie zu erwarten, hat sich nVidia dabei ausschließlich um professionelle Anwendungen, primär im HPC-Bereich gelegen, gekümmert – allerdings wird Ampere nachfolgend auch in den Gaming-Bereich gehen, spätere Ampere-Chips also auch GeForce-Grafikkarten befeuern, wie Videocardz auf Basis einer nVidia-Aussage notieren. Doch selbst aus reiner Architektur-Sicht war die Vorstellung ziemlich mager, denn nVidia hat faktisch nur konkrete Profi-Produkte vorgestellt, weder die Architektur wirklich ausgeblättert noch den ersten Ampere-Grafikchip "GA100" selber (innerhalb der Video-Serie) irgendwie betrachtet. Somit kann man derzeit nur von der HPC-Lösung "A100" sowie den offiziellen Blockdiagrammen auf die Daten des zugrundeliegenden GA100-Chips schlußfolgern – was zumindest einen ersten Überblick zum GA100-Chip erlaubt.

|

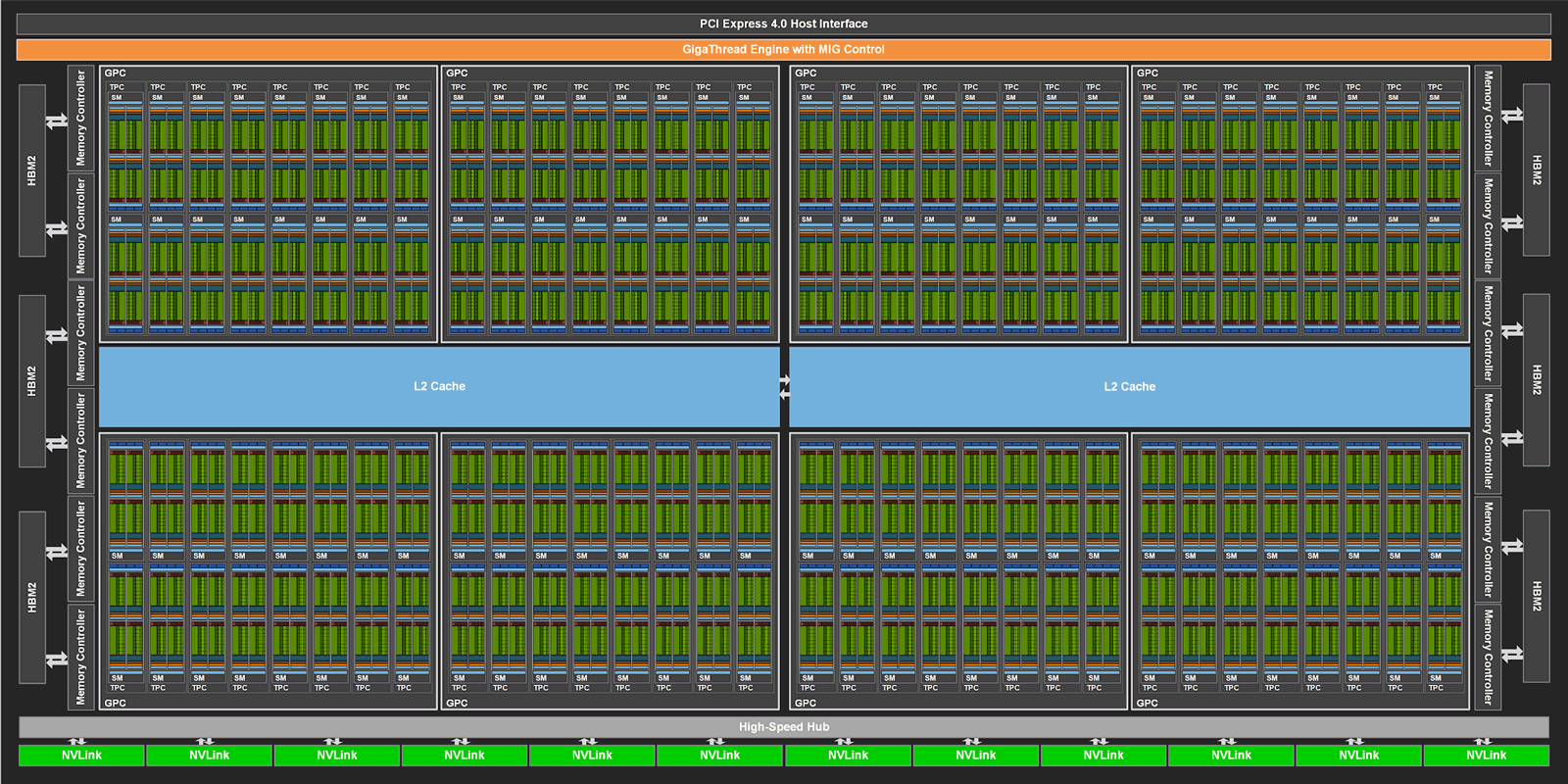

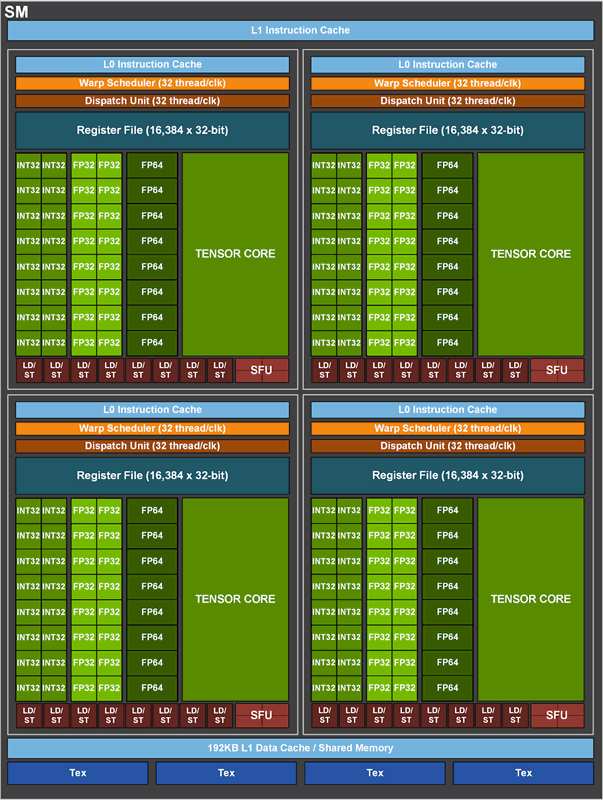

Ganz offiziell wurden die Fertigungsdaten zum GA100 genannt, welcher mit 54 Milliarden Transistoren mehr als doppelt so groß wie sein Vorgänger "GV100" aus der Volta-Generation ist. Die Chipfläche geht leicht von 815mm² (GV100) auf 826mm² (GA100) hinauf, hierfür setzt nVidia die standardmäßige 7nm-Fertigung seitens TSMC (N7) an (beiden Angaben wurden im übrigen seitens der Gerüchteküche korrekt vorhergesagt). Aus den Blockdiagrammen lassen sich dann die schon im letzten November prophezeiten 8 GPCs mit 128 Shader-Clustern und 8192 Shader-Einheiten an einem 6144 Bit breitem HBM2-Speicherinterface ablesen. Die von nVidia vorgestellte HPC-Lösung "A100" führt davon allerdings nur 6912 Shader-Einheiten an einem 5120 Bit HBM2-Interface ins Feld, entspricht also (bei weitem) nicht dem GA100-Vollausbau. Selbigen wird es aber vermutlich sowieso nie in regulären Produkten geben, denn bei solcherart Riesenchips sind die Chancen auf einzelne Silizium-Fehler einfach zu hoch, womit man üblicherweise selbst die Spitzenmodelle immer mit deaktivierten Chipteilen plant.

Zur eigentlichen Ampere-Architektur hat nVidia kaum etwas gesagt, die Betonung bei nVidias Vorträgen lag auf den (stark) verbesserten Tensor-Fähigkeiten der GA100-basierten "A100" HPC-Lösung. Jene verbesserten Tensor-Fähigkeiten dürften sicherlich auch für Gaming-Ampere übernommen werden – aber bei diesem sind dann auch noch andere Architektur-Details wichtig, welche derzeit noch nicht angesprochen wurden bzw. nächste Woche im Rahmen eines technischen "Deep Dive" nachgeholt werden sollen. Aus Gaming-Sicht waren nVidias Vorträge und Pressemitteilungen noch weniger ergiebig, denn der GA100-Chip wird wie sein GV100-Vorgänger augenscheinlich rein im Profi-Segment Verwendung finden. Aufgrund der wohl fehlenden RayTracing-Eignung ist hierbei noch nicht einmal die Zweitverwendung als Titan-Lösung denkbar (die seinerzeitige Titan V auf GV100-Basis kam noch vor dem RTX-Zeitalter). Insofern läßt sich derzeit sehr wenig aus dieser Vorstellung auf Gaming-Ampere übernehmen – noch dazu wo überhaupt nicht garantiert ist, das die nachfolgenden Gaming-Chips von Ampere (GA102 bis GA107) alle Features bzw. Neuerungen des GA100-Chips genauso tragen.

Da nVidia sich zu Gaming-Ampere augenscheinlich noch überhaupt nicht äußern wollte, bleiben weiterhin die bisherigen Prognosen intakt, welche die Ampere-basierte "GeForce 30" Grafikkarten-Serie nicht vor dem Herbst sehen. Vorteilhafterweise könnten die Leaks der nachfolgenden Zeit dann aber eher in Richtung Gaming-Ampere gehen, da der GA100-Chip für den HPC-Bereich nunmehr schließlich bereits vorgestellt wurde. Im übrigen haben sich die GA100-bezogenen Leaks seitens Twitterer 'Kopite7kimi' (No.1 & No.2), welche im Original allesamt bereits aus dem 2019er Sommer (!) stammen, bisher nahezu perfekt bestätigt – einzig allein die doppelte Anzahl an Tensor-Cores ist nicht eingetreten, dafür aber eine Performance-Vervielfachung im Tensor-Bereich, was auch irgendwie passend ist. Dies nährt natürlich den leichten Verdacht, das die Angaben jenes Twitterers zu den weiteren Ampere-Chips genauso korrekt sind – auch wenn dies bedeutet, das der Sprung gegenüber der aktuellen Turing-Generation im Gaming-Bereich deutlich kleiner ausfallen könnte als im HPC-Bereich zwischen Volta und Ampere.

| Original-Aussage von Kopite7kimi | spätere Anmerkung | = Hardware-Konfiguration | |

|---|---|---|---|

| GA100 | TSMC 7EUV, 8GPC*8TPC*2SM 6144bit | - | 128 SM @ 6144 Bit HBM2 |

| GA101 | TSMC 7EUV, 4GPC*8TPC*2SM 3072bit | Chip gestrichen | 64 SM @ 3072 Bit HBM2 |

| GA102 | Samsung 8EUV, 7GPC*6TPC*2SM 384bit, NVLink | realisiert in Samsung 10nm | 84 SM @ 384 Bit GDDR6 |

| GA103 | Samsung 8EUV, 6GPC*5TPC*2SM 320bit | - | 60 SM @ 320 Bit GDDR6 |

| GA104 | Samsung 8EUV, 6GPC*4TPC*2SM 256bit | - | 48 SM @ 256 Bit GDDR6 |

| GA106 | Samsung 8EUV, 3GPC*5TPC*2SM 192bit | - | 30 SM @ 192 Bit GDDR6 |

| GA107 | Samsung 8EUV, 2GPC*5TPC*2SM 128bit | - | 20 SM @ 128 Bit GDDR6 |

| GPC = Graphics Processing Clusters, TPC = Texture Processing Clusters, SM = Streaming Multiprocessors basierend auf den Ausführungen von Kopite7kimi @ Twitter vom 21. Mai 2019 (samt späteren Anmerkungen) |

|||

Nachtrag vom 15. Mai 2020

ComputerBase und PC Games Hardware haben sich nochmals genauer mit dem Spezifikationen des GA100-Chips beschäftigt – nachdem nVidia die Fachpresse im Vorfeld seiner GTC-Keynote nur mit Daten zum A100 HPC-Beschleuniger versorgt hatte und daher zur anfänglichen Verwirrung beitrug, was der "A100" nun genau ist ("nur" ein Produkt) und wie der zugrundeliegende Grafikchip tatsächlich aufgebaut ist. Dabei ergab sich u.a. die wichtige Information, das es tatsächlich keine Hardware-RayTracing-Einheiten auf dem GA100-Chip gibt – wie der vorhergehende HPC-Chip "GV100" kann der GA100-Chip RayTracing dann also nur im Software-Modus, ergo langsamer ausführen. Dies kann bei maßvollem RayTracing-Einsatz durchaus zu spielbaren Frameraten reichen (wie seinerzeit der Fall der Titan V unter Battlefield V mit RayTracing zeigte), aber wirklich werben kann man damit natürlich nicht – womit schon allein aus diesem Grund eine GA100-basierte Gaming-Grafikkarte auszuschließen wäre. Hinzu kommt nun noch der Punkt, das dem GA100-Chip auch die NVENC-Videoeinheit fehlt, womit der Einsatz als reguläre PC-Grafikkarte faktisch auszuschließen ist.

Derweilen ist auffällig, das der GA100-Chip in der 7nm-Fertigung von TSMC (anscheinend die allereinfachste DUV-Variante "N7") eine drastisch höhere Packdichte aufweist als andere 7nm-Grafikchips – mit 65,4 Mio. Transistoren pro mm² immerhin +60% mehr als bei Navi 10 bzw. sogar +64% mehr als bei Vega 20. Natürlich kommt hier die supergroße Chipfläche der Sache entgegen, weil somit schlecht skalierbare Chipteile wie Speichercontroller, Interfaces & Display-Einheit relativ gesehen immer weniger Platz belegen. Trotzdem ist der Vorteil an Transistorendichte viel zu hoch, als dass dies nur damit erklärbar wäre – entweder hat nVidia gezaubert oder AMD hingegen Potential liegengelassen. Aber dies ergibt natürlich auch Chancen zugunsten zukünftiger Navi-Chips unter der 7nm-Fertigung, welche unter den zuletzt kolportierten Chipflächen dann deutlich mehr an Hardware-Einheiten unterbringen könnten, als bislang vermutet wurde. In jedem Fall zeigt nVidia hiermit auf, was unter der 7nm-Fertigung wirklich möglich ist: Der Vorteil in der Transistorendichte gegenüber der 16nm-Fertigung liegt bei dem ca. 2,6fachen – was der allgemeinen Maßgabe entspricht, das zwischen 16nm und 7nm nicht ganz zwei Vollnodes liegen.

| Generation | Fertigung | Chip-Daten | Packdichte | |

|---|---|---|---|---|

| nVidia GP100 | Pascal | 16nm TSMC | 15,3 Mrd. Transistoren auf 610mm² | 25,1 Mio. Tr./mm² |

| nVidia GV100 | Volta | 12nm TSMC | 21,1 Mrd. Transistoren auf 815mm² | 25,9 Mio. Tr./mm² |

| AMD Vega 20 | Vega | 7nm TSMC | 13,2 Mrd. Transistoren auf 331mm² | 39,9 Mio. Tr./mm² |

| AMD Navi 10 | Navi 1X | 7nm TSMC | 10,3 Mrd. Transistoren auf 251mm² | 41,0 Mio. Tr./mm² |

| nVidia GA100 | Ampere | 7nm TSMC | 54 Mrd. Transistoren auf 826mm² | 65,4 Mio. Tr./mm² |

Verwandte News

- OpenCL-Benchmarks sehen AMDs 28nm-Grafikchips gleichauf mit nVidias 16nm-Grafikchips

- nVidia erklärt "Mixed Precision"

- nVidia verspricht 4 TFlops DP für Pascal, 7 TFlops DP für Volta

- AMDs Boltzmann-Initiative geht direkt gegen nVidias CUDA

- nVidias "Big Chips" GK210, GM200 & GP100 bestätigt

- ComputeShader Raytracing Benchmarks verschiedener Grafikkarten

- Gerüchteküche: Erste Hardware-Daten zu den GA104-basierten GeForce RTX 3070 & 3070 Ti Grafikkarten

- Möglicherweise erstes Benchmark-Ergebnis einer "Ampere" Gaming-Grafikkarte aufgetaucht

- Die Grafikchip- und Grafikkarten-Marktanteile im ersten Quartal 2020

- AMD verschiebt Zen 3 angeblich auf Anfang 2021