Hauptlinks

Suchen

nVidia stellt den "GH100"-Chip der Hopper-Generation mit 18'432 FP32-Einheiten in 144 Shader-Clustern vor

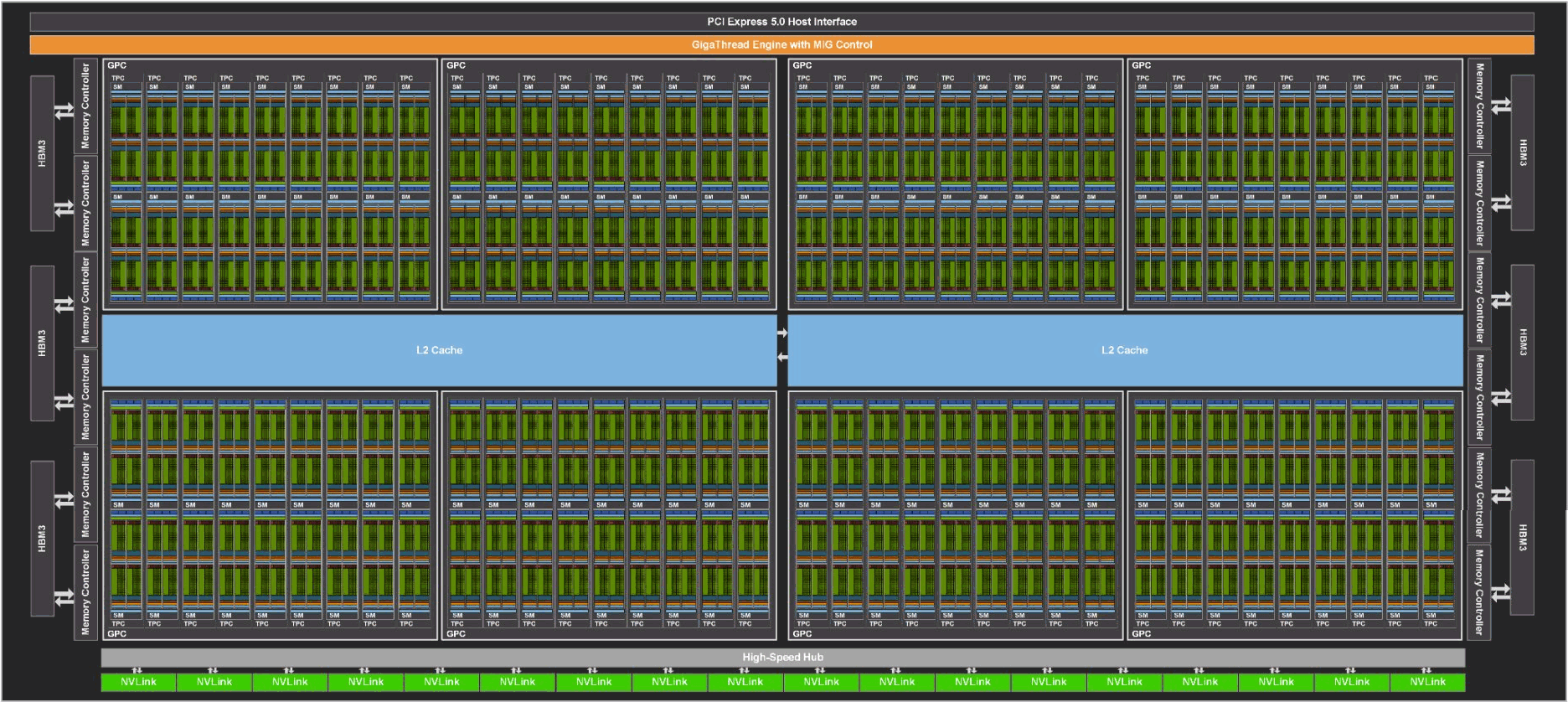

Chipentwickler nVidia hat mit seiner GTC-Keynote die nächste Grafikchip-Generation rund um die 5nm-Fertigung eingeläutet – durch die Vorstellung des "GH100" GPGPU/HPC-Chips auf Basis der "Hopper"-Architektur. Hierbei handelt es sich um den nächsten reinen HPC-Chip von nVidia, sprich in Fortführung des mit der "Pascal"-Architektur begonnenen Wegs reiner HPC-Chips an der Angebots-Spitze: Zuerst GP100 von "Pascal", dann GV100 von "Volta" und GA100 von "Ampere" (trotz gleichen Architektur-Namens deutlich abweichend von den Gaming-Chips dieser Architektur) – und nun eben GH100 von "Hopper". Dabei ist spätetens ab dem GA100-Chip die Zweitverwendung im Gaming-Segment effektiv verbaut, denn GA100 und nun auch GH100 verfügen über keine RayTracing-Einheiten in Hardware – womit entsprechende Gaming-Auskopplungen auf dieser Chip-Basis heutzutage nicht mehr verkaufbar wären.

|

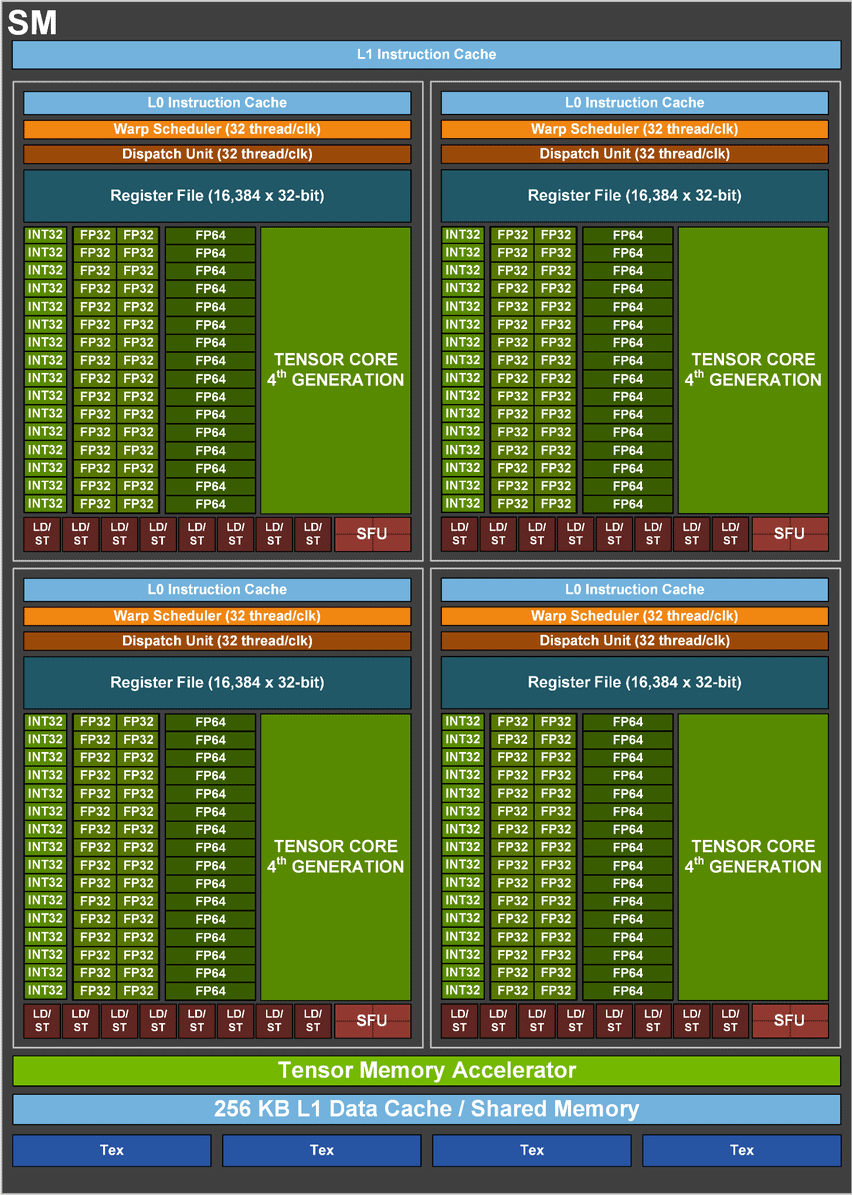

Interessanterweise hat sich die Gerüchteküche im Fall des GH100-Chip mehrfach maßgeblich getäuscht bzw. wurden teilweise gänzlich andere Hardware-Daten vermutet. Korrekt vorhergesagt wurden allein die insgesamt 18'432 FP32-Einheiten, der Weg dahin verläuft jedoch anders als gedacht: So gibt es keinerlei MCM-Ansatz, jener wäre auch angesichts der bis zu 700 Watt TDP im GH100-Spitzenprodukt nicht realistisch. Die 18'432 FP32-Einheiten kommen tatsächlich aus den "nur" 144 Shader-Clustern des GH100-Chips, welcher nunmehr von Gaming-Ampere die FP32-Verdopplung übernimmt: 128 anstatt 64 FP32-Einheiten pro Shader-Cluster. Bisher dachte man, nVidia hätte dieses Feature beim GA100-Chip bewußt weggelassen, weil eventuell unter HPC-Bedingungen nicht nutzvoll – eine Erklärung, die sich mit dem GH100-Chip nunmehr in Luft auflöst. Vermutlich hatte nVidia seinerzeit beim GA100-Chip schlicht nicht die Platzreserven, um auch noch eine FP32-Verdopplung einzubauen.

Stichwort Chipfläche: Auch hier irrte die Gerüchteküche, welche entweder weniger (730mm²) oder viel mehr (bis zu 1000mm²) für den GH100-Chip annahm: Real sind es nunmehr 814mm², was nVidia-typisch nahe am Größenlimit der TSMC-Fertigung (Reticle Limit bei angeblich 858mm²) liegt. Selbst diese Chipgröße ist wahrscheinlich nur möglich über die benutzte 4nm-Fertigung von TSMC als gewisse Verbesserung des 5nm-Nodes (6% höhere Packdichte mit N4 gegenüber N5). Immerhin packt nVidia 80 Milliarden Transistoren in den GH100-Chip, gemäß der verhältnismäßig kleinen Einheiten-Steigerung von 128 auf 144 Shader-Cluster ist dies gegenüber den 54,2 Mrd. Transistoren des GA100-Chips ein ziemlich großer Sprung. Trotzdem reicht es nur für eine gegenüber dem GA100-Chip um +50% verbesserte Packdichte (zwischen TSMC N7 und N4), was allerdings durch die vielen Caches und Interfaces dieser HPC-Chips wohl immer etwas verzerrt wird. Vielleicht ist die Packdichte des GA100-Chips aber auch eher außergewöhnlich gut und damit ein Einzelfall, bei der (hochgerechneten) Anzahl an Transistoren pro FP32-Einheit ist der GH100-Chip nunmehr wieder viel näher an anderen GPGPU-Chips dran.

| Generation | Fertigung | Chip-Daten | Packdichte | SM/CU | Xtor pro FP32 | |

|---|---|---|---|---|---|---|

| nVidia GP100 | Pascal | 16nm TSMC | 15,3 Mrd. Tr. auf 610mm² | 25,1 Mio. Tr./mm² | 60 SM, 3840 FP32 | 4,0 Mio Tr./FP32 |

| nVidia GV100 | Volta | 12nm TSMC | 21,1 Mrd. Tr. auf 815mm² | 25,9 Mio. Tr./mm² | 84 SM, 5376 FP32 | 3,9 Mio Tr./FP32 |

| AMD Vega 20 | Vega | 7nm TSMC | 13,2 Mrd. Tr. auf 331mm² | 39,9 Mio. Tr./mm² | 64 CU, 4096 FP32 | 3,2 Mio Tr./FP32 |

| nVidia GA100 | Ampere | 7nm TSMC | 54,2 Mrd. Tr. auf 826mm² | 65,6 Mio. Tr./mm² | 128 SM, 8192 FP32 | 6,6 Mio Tr./FP32 |

| AMD Arcturus | CDNA1 | 7nm TSMC | 25,6 Mrd. Tr. auf 750mm² | 34,1 Mio. Tr./mm² | 128 CU, 8192 FP32 | 3,1 Mio Tr./FP32 |

| AMD Aldebaran | CDNA2 | 6nm TSMC | 2x 29,1 Mrd. Tr. auf 2x 717mm² | 40,6 Mio. Tr./mm² | 2x 128 CU, 16'384 FP32 | 3,6 Mio Tr./FP32 |

| nVidia GH100 | Hopper | 4nm TSMC | 80 Mrd. Tr. auf 814mm² | 98,3 Mio. Tr./mm² | 144 SM, 18'432 FP32 | 4,3 Mio Tr./FP32 |

Erwähnenswert ist zudem die 4. Generation an Tensor-Einheiten, welche nachfolgend womöglich von der "Ada"-Generation im Gaming-Bereich übernommen werden könnte. Die neuen Tensor-Einheiten beherrschen nunmehr auch FP8 und scheinen zudem die FP32-Verdopplung mitgemacht haben, denn nVidia gibt für jene generell die gut dreifache Rohperformance gegenüber dem GA100-Chip an. Derzeit sind dies allerdings nur Vorhersagen, denn nVidia hat die finalen Taktraten der ersten GH100-Produkte mit dem Produktnamen "H100" (sprich ohne das anführende "G") noch nicht festgelegt. Die von nVidia offerierten Rohleistungs-Angaben rechnen augenscheinlich mit 1775 MHz Chiptakt – was deutlich über den maximal 1410 MHz der Vorgänger-Lösung liegt, allerdings klar unterhalb der Taktraten-Möglichkeiten für dieses Fertigungsverfahren bei Gaming-Grafikchips. Da nVidia erste Auslieferungen an "H100" GPGPU/HPC-Lösungen erst im dritten Quartal 2022 vornehmen will, bleibt sowieso noch einige Zeit, um zu finalen Taktraten zu finden.

| A100 SXM4 (Ampere) | H100 SXM5 (Hopper) | |

|---|---|---|

| aktive Shader-Cluster | 108 von 128 (84%) | 132 von 144 (92%) |

| Chiptakt | max. 1410 MHz | 1775 MHz (nicht final!) |

| Peak FP8 Tensor (Accumulate) /mit Sparsity | nicht verfügbar | 2000/4000 TFlops |

| Peak FP16 Tensor (Accumulate) /mit Sparsity | 312/624 TFlops | 1000/2000 TFlops (x3,2) |

| Peak BF16 Tensor (Accumulate) /mit Sparsity | 312/624 TFlops | 1000/2000 TFlops (x3,2) |

| Peak TF32 Tensor /mit Sparsity | 156/312 TFlops | 500/1000 TFlops (x3,2) |

| Peak FP64 Tensor | 19,5 TFlops | 60 TFlops (x3,1) |

| Peak INT8 Tensor /mit Sparsity | 624/1248 TOPs | 2000/4000 TOPs (x3,2) |

| Peak FP16 non-Tensor | 78 TFlops | 120 TFlops (x1,5) |

| Peak BF16 non-Tensor | 39 TFlops | 120 TFlops (x3,1) |

| Peak FP32 non-Tensor | 19,5 TFlops | 60 TFlops (x3,1) |

| Peak FP64 non-Tensor | 9,7 TFlops | 30 TFlops (x3,1) |

| Peak INT32 | 19,5 TOPs | 30 TOPs (x3,1) |

| TDP | 400 Watt | 700 Watt (x1,75) |

In der Summe hat nVidia sein neues Rechenmonster somit nicht über einen MCM-Ansatz, sondern über die FP32-Verdopplung erreicht. Zuzüglich gewisser Steigerungen bei Chiptakt und Einheiten-Anzahl führt dies letztlich zu einer 3fach höheren Rohleistung in den allermeisten Disziplinen – ein überhaus starkes Leistungsplus für nur eine Chip-Generation, erzielt zudem über einen vergleichsweise konservativen Ansatz. Allerdings gibt es immer irgendwo einen Haken – und jener liegt beim GH100-Chip im explodierenden Stromverbrauch: Die SXM-Variante wird von nVidia mit gleich 700 Watt TDP genannt – fast das Doppelte gegenüber dem Ampere-Vorgänger. Dies zeigt darauf hin, dass TSMCs 5nm-Node (samt dessen 4nm-Derivat) zwar zu Höchstleistungen in der Lage ist, jene aber nicht gerade Stromverbrauchs-neutral ableisten kann. Somit besteht weiterhin die Befürchtung, dass auch die kommenden Gaming-Grafikchips auf Basis der 5nm-Fertigung ein ähnliches Verhalten zeigen: Ein hoher Performance-Sprung, jedoch gekoppelt mit weiter steigendem Strombedarf.

Verwandte News

- nVidia stellt den "GA100"-Chip der Ampere-Generation mit 8192 Shader-Einheiten an einem 6144 Bit HBM2-Interface vor

- OpenCL-Benchmarks sehen AMDs 28nm-Grafikchips gleichauf mit nVidias 16nm-Grafikchips

- nVidia erklärt "Mixed Precision"

- nVidia verspricht 4 TFlops DP für Pascal, 7 TFlops DP für Volta

- AMDs Boltzmann-Initiative geht direkt gegen nVidias CUDA

- nVidias "Big Chips" GK210, GM200 & GP100 bestätigt

- ComputeShader Raytracing Benchmarks verschiedener Grafikkarten

- Neuer Artikel: Grafikkarten-Marktüberblick November 2023

- Gerüchteküche: GeForce RTX 40 Refresh-Lösungen mit zumeist derselben TDP

- Gerüchteküche: Dritte Portfolio-These zum GeForce RTX 40 Refresh aufgetaucht