Hauptlinks

Suchen

GPGPU

AMD auf der CES 2023: Ryzen 7000 non-X, X3D & Mobile, Radeon RX 7600 M/S und Instinct MI300

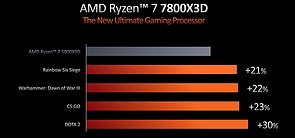

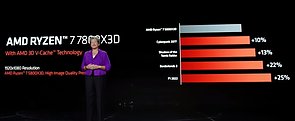

Mit seiner CES-Keynote (als Video bei YouTube oder als bebilderter Live-Blog bei TechPowerUp) hat AMD ein umfangreiches, aktualisiertes Produkt-Portfolio für den Jahresbeginn 2023 vorgestellt. Enthalten war dabei alles, was man sich erwarten konnte, sogar inklusive der offiziellen Vorstellung dreier Modelle von Ryzen 7000 X3D. Mit konkreten Daten war AMD hingegen sparsam, jene gab es zumeist erst nachfolgend mittels Pressemitteilungen sowie den entsprechenden Produkt-Webseiten. Trotzdem blieben einige Wissenslücken gerade zu Ryzen 7000 X3D zurück: So nannte AMD keine Listenpreise, PPT-Werte und konkreten Release-Termine. Offiziell sind jene bei AMD im übrigen als "veröffentlicht am 4. Januar 2023" eingebucht, real werden jene Prozessoren aber erst in diesem Februar erscheinen. Dann wird man sehen müssen, wie die etwas niedrigeren Taktraten und TDPs (nur 120W, gegenüber ansonsten 170W) im Spiele-Feld zu verkraften sind – für etwas anderes sind jene Prozessoren augenscheinlich überhaupt nicht gedacht.

AMD zeigt neue CPU/GPU-Roadmaps sowie Ausblicke auf Zen 4 & RDNA3

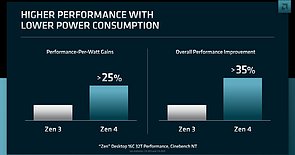

Auf seinem Financial Analyst Day (FAD) des Jahres 2022 hat AMD einen umfangreichen Schwung an neuen Roadmaps für alle Unternehmens-Bereiche herausgebracht – welche auch endlich einmal über den bisherigen Maximalstand hinausgehen, welcher (bisher) schließlich schon im Jahr 2022 endete. Die längsten der neuen AMD-Roadmaps gehen nun bis zum Jahr 2024, womit endlich einmal RDNA4 und Zen 5 ganz offiziell von AMD genannt wurden. Alle Roadmaps bringen wie üblich keine genauen Terminangaben mit sich, sondern nur ein Enddatum – welches wie bei früheren AMD-Roadmaps das jeweilige Jahresende abbildet. Eine Roadmap, die mit dem Jahr 2024 endet, zeigt also an, dass alle eingezeichneten Produkte bis zum Ende des Jahr 2024 herausgebracht werden sollen. Das Hauptaugenmerk der dargebrachten Präsentationsfolien galt allerdings sowieso den dieses Jahr noch anstehenden AMD-Produkten, im CPU-Bereich ist dies "Zen 4".

nVidia stellt den "GH100"-Chip der Hopper-Generation mit 18'432 FP32-Einheiten in 144 Shader-Clustern vor

Chipentwickler nVidia hat mit seiner GTC-Keynote die nächste Grafikchip-Generation rund um die 5nm-Fertigung eingeläutet – durch die Vorstellung des "GH100" GPGPU/HPC-Chips auf Basis der "Hopper"-Architektur. Hierbei handelt es sich um den nächsten reinen HPC-Chip von nVidia, sprich in Fortführung des mit der "Pascal"-Architektur begonnenen Wegs reiner HPC-Chips an der Angebots-Spitze: Zuerst GP100 von "Pascal", dann GV100 von "Volta" und GA100 von "Ampere" (trotz gleichen Architektur-Namens deutlich abweichend von den Gaming-Chips dieser Architektur) – und nun eben GH100 von "Hopper". Dabei ist spätetens ab dem GA100-Chip die Zweitverwendung im Gaming-Segment effektiv verbaut, denn GA100 und nun auch GH100 verfügen über keine RayTracing-Einheiten in Hardware – womit entsprechende Gaming-Auskopplungen auf dieser Chip-Basis heutzutage nicht mehr verkaufbar wären.

|

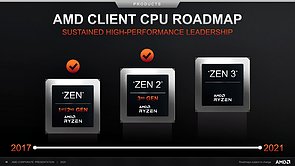

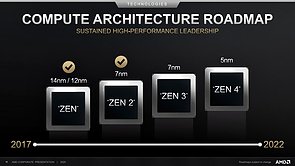

Aktualisierte AMD-Roadmaps zeigt "Zen 4" im Consumer-Bereich nicht vor dem Jahr 2022 an

AMD hat im Zusammenhang mit seinen jüngsten Quartalszahlen auch eine neue "Unternehmens-Präsentation" (PDF) herausgegeben, welche u.a. alle offiziellen AMD-Roadmaps in aktualisierter Form enthält. Dazu gibt es eigentlich keinerlei bahnbrechende Neuigkeiten zu berichten – um so mehr verwundern dann Meldungen, wonach AMD mit diesen Roadmaps angeblich Zen 4 und RDNA3 bereits für das Jahr 2021 "bestätigt" haben soll. Dies wäre selbigen Roadmaps aber nur dann zu entnehmen, sofern man die Roadmap-Zeitskala als jeweils tagesgenaue Zeitpunkte interpretiert. Eine AMD-Roadmap mit eingezeichneter Zeitskala von "2017 bis 2021" endet aber nicht am 1. Januar 2021 (womit alle eingezeichneten Produkte noch bis Ende 2020 herauskommen müssten) – sondern natürlich endet diese Roadmap am 31. Dezember 2021, da mit den Jahresangaben jeweils immer das komplette Jahr gemeint ist. Eine indirekte Bestätigung für diese Auslegung findet sich in einem früheren AnandTech-Artikel, wo AMD auf Nachfrage das Zeitskalen-Ende "2021" mit "end of 2021" gleichsetzte. Eine andere Bestätigung ergibt sich über frühere AMD-Roadmaps, wo "Zen 3" rein optisch noch vor dem Jahr 2020 eingezeichnet wurde – logisch, dass die Jahresangabe dort nur als "Gesamtjahr 2020" und nicht als "Jahresstart 2020" gemeint sein konnte.

nVidia stellt den "GA100"-Chip der Ampere-Generation mit 8192 Shader-Einheiten an einem 6144 Bit HBM2-Interface vor

Mit einer Serie von 12 Videos hat nVidia seine für die abgesagte GTC im März angesetzte GTC-Keynote in Form der Vorstellung erster Ampere-basierter Produkte nachgeholt. Wie zu erwarten, hat sich nVidia dabei ausschließlich um professionelle Anwendungen, primär im HPC-Bereich gelegen, gekümmert – allerdings wird Ampere nachfolgend auch in den Gaming-Bereich gehen, spätere Ampere-Chips also auch GeForce-Grafikkarten befeuern, wie Videocardz auf Basis einer nVidia-Aussage notieren. Doch selbst aus reiner Architektur-Sicht war die Vorstellung ziemlich mager, denn nVidia hat faktisch nur konkrete Profi-Produkte vorgestellt, weder die Architektur wirklich ausgeblättert noch den ersten Ampere-Grafikchip "GA100" selber (innerhalb der Video-Serie) irgendwie betrachtet. Somit kann man derzeit nur von der HPC-Lösung "A100" sowie den offiziellen Blockdiagrammen auf die Daten des zugrundeliegenden GA100-Chips schlußfolgern – was zumindest einen ersten Überblick zum GA100-Chip erlaubt.

|

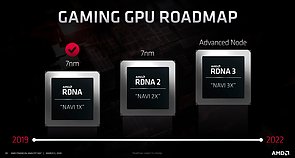

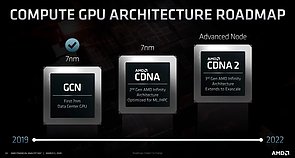

Neue Grafik-Roadmaps von AMD reichen bis zu RDNA3, Navi 3X & CDNA2 im Jahr 2022

Auf seinem "Financial Analyst Day" (FAD'20) hat AMD neue Grafik-Roadmaps ausgepackt, welche seit längerem mal wieder neue Eintragungen die zukünftige Entwicklung betreffen. Die wichtigste Neuerung liegt allerdings darin, das AMD sich zu einer echten Auftrennung von Gaming-Grafik und Compute-Grafik entschlossen hat – letztere bekommt nunmehr mittels der "Compute RDNA" (CDNA) eine eigene Architektur-Klasse und damit eine eigene Roadmap. Dies ermöglicht nicht nur im symbolischen, sondern auch ganz praktischen Sinn eine vollständig getrennte Weiterentwicklung der jeweiligen Chips – mit natürlich auch der Folge, das die Produkte nicht mehr im jeweils anderen Produktsegment zweitverwendet werden können. Ein erster klarer Schritt in diese Richtung hin dürfte der kommende "Arcturus"-Chip sein, welcher zwar auf dem FAD'20 nicht konkret genannt wurde, dennoch aber augenscheinlich der CDNA1-Generation zuzuordnen ist (während die Vega-20-basierten Compute-Beschleuniger noch zur GCN-Generation gehören).

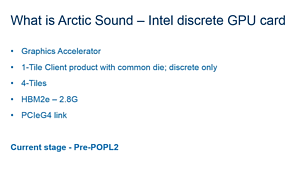

Intel-Dokumente zeigen auf "Arctic Sound" Xe-Grafiklösungen mit bis zu 512 EU samt HBM2E- und PCIe4.0-Interfaces

Digital Trends zeigen einige Intel-Dokumente zur kommenden "Arctic Sound" Grafik-Generation, mit welcher Intel die Xe-Architektur nach dem "Testlauf" mit DG1 wohl nächstes Jahr so richtig starten will. Hieraus wird eine gewisse Einschätzung dessen möglich, was Intel mit Arctic Sound letztlich bringen könnte, teilweise werden sogar frühere Gerüchte untermauert – und dennoch bleiben natürlich noch viele Fragen offen. Unbestätigt und somit unsicher bleibt beispielsweise, ob die von Intel angesetzte Unterteilung von Arctic Sound in bis zu vier "Tiles" wirklich einer Unterteilung in einzelne Chiplets entspricht. Zwar geht Intel bei seiner HPC-Auskopplung "Ponte Vecchio" augenscheinlich diesen Weg, aber für normale Grafikkarten mit der Zielsetzung einer Grafik- und Videoausgabe ist die hiermit einhergehende Problematik der effektiven Zusammenarbeit von einzelnen Chiplets (außerhalb von reinen GPGPU-Aufgaben) immer noch nicht zufriedenstellend gelöst. In jedem Fall entsprechen die genannten drei Ausführungen von Arctic Sound mit 1, 2 oder 4 Tiles dann allerdings früheren Gerüchten über Intel-Grafiklösungen der zweiten Generation (DG2) mit 128, 256 und 512 EUs (Execution Units).

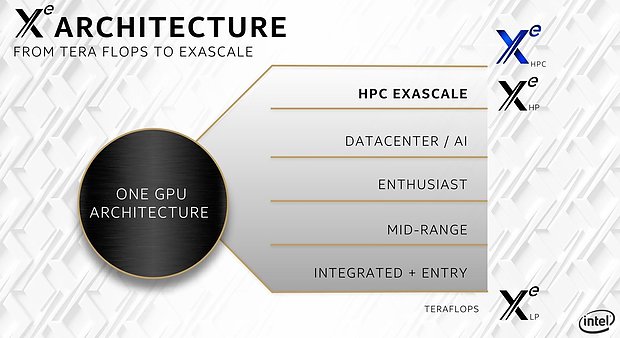

Intels Xe-Grafik teilt sich in drei Architekturen für alle Anwendungs-Bereiche auf

Intels Raja Koduri hat bei der Intel-Präsentation auf der HPC-Konferenz "SC19" Intels nächste HPC-Projekte angekündigt – darunter auch eine Xe-basierte Exascale-Grafiklösung, womit unvermeidlicherweise auch etwas zu dieser kommenden Intel-Grafik gesagt wurde. So wurde "Xe" nunmehr als Oberbegriff für alle zukünftigen Grafik-Aktivitäten von Intel (ab Intels Grafik-Generation 12) ausgegeben, dürfte somit auch für zukünftige Grafik-Generationen von Intel übernommen werden. Hieraus folgen dann drei Architekturen für verschiedene Anwendungszwecke: "Xe LP" für integrierte sowie Einsteiger-Lösungen, "Xe HP" für das Midrange- bis Enthusiasten-Segment sowie Datacenter/AI-Lösungen und letztlich "Xe HPC" für reine HPC-Lösungen im Exascale-Bereich. Intel betrachtet dies als jeweils getrennte Architekturen, technisch dürfte man wohl eher von Abwandlungen derselben Architektur sprechen können, da die Grundbausteine innerhalb derselben Generation sicherlich dieselben sein dürften.

OpenCL-Benchmarks sehen AMDs 28nm-Grafikchips gleichauf mit nVidias 16nm-Grafikchips

Im Benchmarking-Teil unseres Forums wird neben vielen anderen Programmen und aktuellen Spielen auch weiterhin MrH's OpenCL-Mark in dessen aktueller Version 1.11 durchgetestet. Hierbei handelt es sich um einen Test der puren Rechenkraft von reinen Grafikchips unter OpenCL – was unter einigen Anwendungen schon verwendet wird und auch im Spielebereich für die Zukunft wichtig werden sollte. Heutige Grafikchips eigenen sich nun einmal sehr gut als Parallelbeschleuniger, was mittels OpenCL ausgenutzt wird, um die verschiedensten Probleme möglichst recheneffizient zu lösen – meistens allerdings welche aus dem professionellen Bereich. Die Adaption in normale Anwendungssoftware ist eher schwierig, da nur Teilaufgaben mittels OpenCL zu beschleunigen sind. Im Spielebereich ist dagegen aufgrund der komplexen Spielwelts-Berechnungen heutiger Titel samt schwer zu jeder Sekunde vollständig auslastbarer Grafikbeschleuniger (theoretisch) ein größerer Ansatzpunkt für die Nutzung von OpenCL zu finden – auch wenn die praktische Nutzung unter Spielen derzeit eher homöopathischer Natur ist. Nichtsdestotrotz ist OpenCL sicherlich eine wichtige Disziplin in der Zukunft, welche heutzutage schon teilweise genutzt wird – die unter OpenCL zu erwartende Performance mißt dann der MrH OpenCL-Mark aus:

Spezifikations-Vergleich Intel Xeon Phi 7200 vs. nVidia Tesla P100

Mit der Vorstellung von Intels neuem Xeon Phi Prozessor auf Knights-Landing-Basis in Konkurrenz zu nVidias GP100-Chip lohnt nunmehr wieder einmal ein Vergleich der verschiedenen HPC-Ansätze der entsprechenden Hersteller – derzeit noch ohne AMD, denn deren entsprechendes Vega-11-Projekt dürfte erst im nächsten Jahr spruchreif werden. Intel hat mit "Knights Landing" mal wieder einen echten Monsterchip mit einer Chipfläche von ~700mm² unter der 14nm-Fertigung hingelegt – und in diese bis zu 76 physikalische Rechenkerne einer hochgeschraubten Silvermont-Architektur gesteckt, womit diese eigentlich für LowPower-Prozessoren gedachte Atom-Architektur einen interessanten Zweitnutzen erfährt. Wie bei nVidias Tesla P100 können die aktuellen Xeon Phi 7200 Lösungen die vorhandene Hardware aus Ausbeutegründen jedoch nicht komplett ausnutzen – die Tesla P100 kommt mit nur 3584 freigeschalteten von 3840 physikalisch vorhandenen Shader-Einheiten daher, Xeon Phi hingegen mit (je nach Modell) zwischen 64 und 72 freigeschalteten von 76 physikalisch vorhandenen x86-Rechenkernen: