Hauptlinks

Suchen

nVidias GP100-Chip mit 4 TFlops DP- und 12 TFlops SP-Rechenleistung geplant?

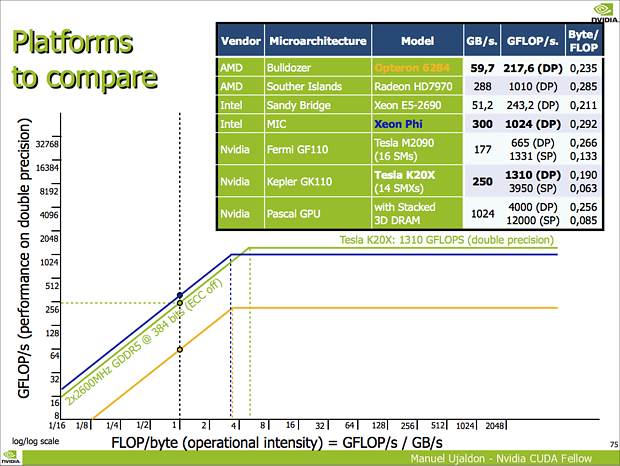

Eine in unserem Forum aufgetauchte Grafik aus einer im Juni 2015 abgehaltenen Präsentation eines CUDA-Fellows (PDF) spricht dem kommenden Pascal-Topchip GP100 immerhin 4 TeraFlops DoublePrecision- sowie 12 TeraFlops SinglePrecision-Rechenleistung bei 1024 GB/sec Speicherbandbreite zu. Da das zugrundeliegende Dokument zumindest halboffiziellen Charakter hat sowie der "CUDA-Fellow" in Form von Manuel Ujaldon ein spanischer Universitätsprofessor mit eigenem Profil auf der nVidia-Webseite ist, dürfte es sich hiermit um Daten handeln, welche nVidia intern selber so kommuniziert haben wird – zumindest zum Stand vom Juni 2015. Mit der Zeit kann sich daran noch einiges ändern – gerade bei den finalen Taktraten – aber der grundsätzliche Aufbau des GP100-Chip muß seinerzeit schon festgestanden haben, schließlich war der Tape-Out des GP100-Chips um diesen Zeitpunkt herum.

Dies wirft allerdings ultimativ die Frage auf, ob nVidia beim GP100-Chip trotz des Mixed-Precision-Features kein DP/SP-Verhältnis von 1:2 bieten wird – sondern ob jenes wieder bei 1:3 liegt (wie bei der Kepler-Architektur, welche allerdings andere Shader-Cluster als die Maxwell-Architektur aufweist). Dies wäre in jedem Fall überraschend und deutet auf einen erneut anderen Aufbau der Shader-Cluster gegenüber der vorhergehenden Maxwell-Architektur hin, eventuell auch erneut die Hinzunahme dedizierte DoublePrecision-Einheiten. Gleichfalls würden die genannten 12 TeraFlops SinglePrecision-Rechenleistung bei einer Profi-Grafikkarte, welche üblicherweise nicht mit voll ausgefahrenen Taktraten antritt, auf einen echten Monsterchip hindeuten. Erreichbar wäre diese enorme Rechenleistung beispielsweise auf rund 1000 MHz Taktrate mit dann 6144 Shader-Einheiten – und damit einer glatten Verdopplung dessen, was der GM200-Chip zu bieten hat (3072 Shader-Einheiten).

Realisierbar erscheint dies durchaus angesichts der Möglichkeiten der 16nm-Fertigung, welche bezüglich der Flächenersparnis gegenüber der 28nm-Fertigung sogar besser liegen soll als nur Faktor 2 – bestenfalls soll Faktor 2,5 erreichbar sein, wobei sich dies eher auf sehr einfache Transistoren bezieht und sicherlich nicht über einen ganzen Grafikchip hinweg durchzuhalten ist. Allerdings kommen beim GP100-Chip dann noch die extra Transistoren für die Profi-Features hinzu, welche beim vorhergehenden GM200-Chip bewußt weggelassen wurden. Etwas einsparen an Transistoren & Chipfläche kann der GP100-Chip dann durch sein HMC- oder HBM-Speicherinterfaces, welches deutlich weniger Platz belegen wird als ein vergleichbares GDDR5- oder GDDR5X-Speicherinterface. Trotzdem würde nVidia dann bei den vorgenannten 6144 Shader-Einheiten schon mit dem allerersten eigenen 16nm-Chip die Möglichkeiten der 16nm-Fertigung von Chiphersteller TSMC bis an die Grenzen ausnutzen, die GP100-Chipfläche ist angesichts dieser Daten auf erneut in der Nähe von 600mm² zu schätzen (GM200 ohne Profi-Features: 601mm²). Dies wäre ebenfalls überraschend viel, bisher ging man von einem eher langsamen Herangehen der Grafikchip-Entwickler an die 14/16nm-Fertigung heran.

Die eigentliche Präsentation drehte sich im übrigen über die Zukunft der Speichertechnologie im HPC-Bereich, bezogen speziell auf nVidias Grafikchips natürlich. Interessanterweise wird dabei immer über "Hybrid Memory Cube" (HMC) gesprochen, HBM ("High Memory Bandwith") hingegen nur einmal in Form eines Vergleichs mit DDR3 und GDDR5 genannt. Aufgrund der relativen Frische der Präsentation (wie gesagt erst im Juni 2015 abgehalten), wollen die Argumente, daß nVidia hier mit HMC dann vielleicht HBM meinen könnte oder auch innerhalb der Pascal-Entwicklung von HMC auf HBM umgeschwenkt wäre, nicht mehr so recht ziehen. Nicht auszuschließen also, daß der GP100-Chip abweichend vom bisherigen Wissenstand tatsächlich doch mit dem zuletzt kaum noch erwähnten HMC antreten wird ("3D-Memory" ist schließlich beides). Gerade, da nVidia ziemlich sicher innerhalb der Pascal-Generation allein den GP100-Chip auf die neue Speichertechnologie umstellen wird, könnte man durchaus diesen Sonderweg gehen – müssen hierbei schließlich keine Befindlichkeiten des breiten Produktprogramms berücksichtigt werden.

Nachtrag vom 17. Februar 2016

Eine andere Auflösung zur Frage, wie die 12 TFlops SinglePrecision-Rechenleistung bei nVidias GP100-Chip erklärbar sind, bieten beispielsweise PC Games Hardware oder auch Videocardz an: Denn natürlich geht dies auch mit weniger als 6144 Shader-Einheiten – rein rechnerisch reichen auch 5120 Shader-Einheiten auf dann 1175 MHz Chiptakt aus. Was ein wenig gegen diese Annahme spricht, sind die damit für Tesla-Beschleuniger ungewöhnlich hohen Taktraten – die Tesla K40 auf GK110-Basis taktet bekannterweise nur mit 745-845 MHz Chiptakt (eine GeForce GTX 780 Ti hingegen mit durchschnittlich 952 MHz). Einzurechnen gilt hierbei vor allem, daß die maximalen Takt-Möglichkeiten des jeweiligen Fertigungsverfahrens im Tesla-Bereich bewußt nicht angestrebt werden – sondern man sich vielmehr nach dem Sweetspot ausrichtet, wo das Verhältnis "Performance pro Stromverbrauch" am besten liegt. So gesehen erscheinen selbst die für 6144 Shader-Einheiten benötigten 980 MHz aus ausreichend hoch für einen neuen Chip unter der (angeblich taktfreudigeren) 16nm-Fertigung.

Jegliche Lösungen mit geringerer Anzahl an Shader-Einheiten und dafür höherem Chiptakt sind deswegen trotzdem nicht raus aus der Diskussion – mit allerdings 5120 Shader-Einheiten als unterstem Grenzwert, weil viel höhere Taktraten (als 1175 MHz) sind bei diesen Profi-Varianten selbst unter der 16nm-Fertigung nicht vorstellbar. Davon abgesehen ergibt diese ungefähre Angabe zur Anzahl der Shader-Einheiten beim GP100-Chip von 5120-6144 Stück leider keinen Hinweis darauf, wie die kleineren Chip der Pascal-Generation aussehen werden. Die alte Regel, daß es nach unten gehend jeweils zumeist glatte Halbierungen der größeren Chips werden, muß zumindest für den GP100-Chip nicht gelten, da jener vermutlich rein im Profi-Segment eingesetzt werden wird. Der Ausgangspunkt für das Consumer-Segment wird vielmehr wahrscheinlich der GP102-Chip sein, zu dessen Daten und vor allem zu dessen Zielsetzung seitens nVidia (Chipfläche und Performanceanspruch) derzeit noch gar nichts bekannt ist.

Verwandte News

- nVidia legt seinen HighEnd-Lösungen "The Division" bei

- nVidia bringt im März mit der "GeForce GTX 950 SE" wohl eine dritte GM206-Variante

- nVidias GP104-Chip womöglich schon in Form kompletter Grafikkarten vorhanden?

- GDDR5X: Nicht mit höheren Taktraten, sondern mit QDR-Datenübertragung

- Umfrage-Auswertung: Auf die 14/16nm-Grafikkarten warten?

- Umfrage-Auswertung: G-Sync vs. FreeSync - was ist bereits im Einsatz, was zieht mehr Interesse an?

- Neuer Artikel: Grafikkarten-Marktüberblick Februar 2016

- Die Grafikkarten-Performance unter Rise of the Tomb Raider

- Umfrage-Auswertung: Welche neue Hardware wird im Jahr 2016 am meisten erwartet?

- GDDR5X-Speicher ist nunmehr offiziell spezifiziert