Hauptlinks

Suchen

Finale Spezifikation 1.0 für PCI Express 6.0 fertiggestellt

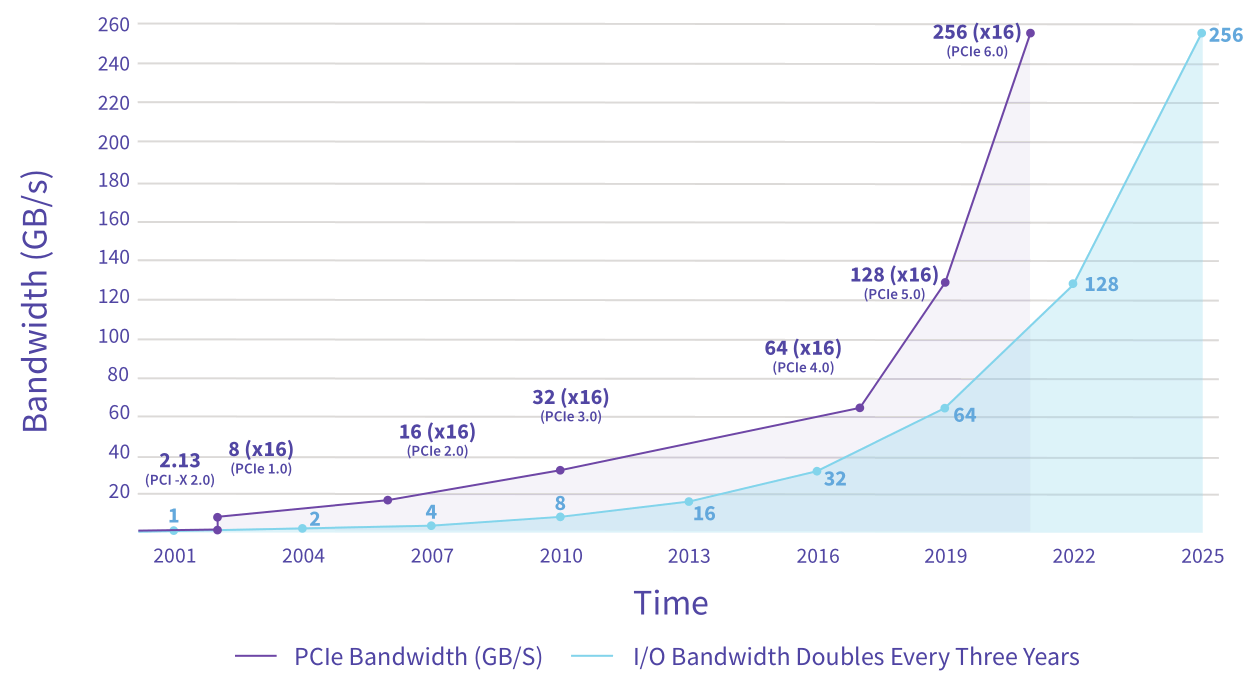

Die "PCI Special Interest Group" (PCI-SIG) vermeldet die Finalisierung der Spezifikation 1.0 für PCI Express 6.0. Mittels PAM4-Signalisierung (4 anstatt 2 Zustände pro Datenübertragung, wie bei GDDR6X-Speicher) verdoppelt sich die Bandbreite gegenüber PCI Express 5.0 erneut. Somit erreicht PCI Express 6.0 mit 16 Lanes eine offizielle Bandbreite von 128 GB/sec pro Richtung – real sind es 120,5 Milliarden Bytes/sec, sprich eigentlich "nur" 112 GB/sec. Wie üblich bei PCI Express bedeutet "Spezifizierung" nicht gleich Markteinsatz: Die finale Spezifikation zu PCI Express 4.0 wurde im Juni 2017 erstellt, die erste breite Anwendung im Consumer-Segment erfolgte allerdings erst im Juli 2019 mittels Zen 2 und RDNA1 (der Vega-20-Chip der Radeon VII konnte schon vorher PCI Express 4.0, dies blieb jedoch professionellen Lösungen vorbehalten).

| x1 | x4 | x8 | x16 | Spezifizierung | Consumer-Produkte | |

|---|---|---|---|---|---|---|

| PCI Express 1.x | ¼ GB/sec | 1 GB/sec | 2 GB/sec | 4 GB/sec | 2003 | ? |

| PCI Express 2.x | ½ GB/sec | 2 GB/sec | 4 GB/sec | 8 GB/sec | Januar 2007 | Oktober 2007 (X38) |

| PCI Express 3.x | 1 GB/sec | 4 GB/sec | 8 GB/sec | 16 GB/sec | November 2010 | April 2012 (Ivy Bridge) |

| PCI Express 4.0 | 2 GB/sec | 8 GB/sec | 16 GB/sec | 32 GB/sec | Juni 2017 | Juli 2019 (Zen 2 & RDNA1) |

| PCI Express 5.0 | 4 GB/sec | 16 GB/sec | 32 GB/sec | 64 GB/sec | Mai 2019 | November 2021 (Alder Lake) |

| PCI Express 6.0 | 8 GB/sec | 32 GB/sec | 64 GB/sec | 128 GB/sec | Januar 2022 | kaum vor 2024 |

| Bandbreiten angegeben als offizielle, nominelle Bandbreite (pro Richtung) | ||||||

Insofern kann man mit wiederum mit mindestens 2 Jahren rechnen, welche die Adaption der neuen PCI-Express-Norm benötigen dürfte. Selbige muß primär in die jeweils aktuellen PC-Prozessoren integriert werden – erst dann ergibt die Auflage von Grafikkarten und SSDs nach PCI Express 6.0 einen Sinn. Da Prozessoren-Entwicklung eine langwierige Sache ist, sind die genannten 2 Jahre schon ein vergleichsweise knapper Zeitraum – dafür müssen die CPU-Entwickler eigentlich schon entsprechende Vorarbeit bei ihren NextGen-Designs geleistet haben. Im Idealfall dürfte dies somit hochgerechnet die PC-Prozessoren des Jahres 2024 betreffen – sprich AMDs Zen 5 oder gar erst Zen 6 sowie Intels Arrow Lake oder Lunar Lake. Irgendwelche belastbaren Hinweise darauf, ab welchem Zeitpunkt AMD & Intel mit der eigenen Adaption von PCI Express 6.0 planen, gibt es allerdings noch nicht.

Generell gilt zu sagen, dass mit der aktuell in den Markt kommenden PCIe 5.0 Norm sowie spätestens dann der PCIe 6.0 Norm aller Vermutung nach eine deutlich Abkehr vom bisherigen Prinzip "16 Lanes für alles" (auf CPU- und GPU-Seite) erwartet werden kann – sondern dass sehr fein austariert wird, welche Lane-Anzahl welches Produkt bekommt. Die Ansätze hierfür sind derzeit schon zu sehen, wenn AMD die PCI-Express-Lanes der RDNA2-Grafikchips klar abstuft oder auch die Mobile-Prozessoren von AMD & Intel üblicherweise nur noch mit 8 Lanes antreten (wie nunmehr auch bei Alder Lake). Insofern betrifft die nominelle Bandbreiten-Verdopplung immer weniger Geräte, könnte oftmals nur noch für Spitzen-Hardware gelten. Insbesondere im Mainstream-Bereich dürfte es sich spätestens mit PCI Express 6.0 etablieren, dass mit weniger Lanes gearbeitet wird – was nicht nur den Stromverbrauch des PCIe-Interfaces begrenzt, sondern auch Platinen- und Verdrahtungs-Aufwand reduziert. Allein Spitzen-Grafikkarten und Spitzen-SSDs dürften unter PCI Express 6.0 auch weiterhin mit der jeweils höchsten Lane-Anzahl (16 bzw. 4) antreten.

Interessant ist daneben, dass die aktuelle PCI-Express-Roadmap keinerlei Weiterentwicklung nach PCIe 6.0 verspricht bzw. ein hypothetisches "PCI Express 7.0" auch nirgendwo anders angedeutet wird. Dies könnte einen gewissen Umschwung nach der schnellen Einführung von PCIe 5.0 & 6.0 (folgend auf PCIe 4.0) anzeigen – sprich, dass es nunmehr wiederum einige Jahre brauchen könnte, ehe eine neue PCIe-Norm nachfolgt. Möglicherweise ist man nach dieser Phase der schnellen Weiterentwicklung nunmehr vorerst an technischen Limitationen angelangt. So wurden für neue PCIe-Normen üblicherweise die Taktraten angehoben, was aber natürlich auch nicht unendlich oft möglich ist. Die PAM4-Signalisierung von PCIe 6.0 deutet in die Richtung, dass es für diese Norm sogar einfacher war, lieber jene durchaus komplizierte Signalisierung anstatt wiederum höheren Taktraten zu verwenden. Dass eines Tages eventuell auftauchende PCI Express 7.0 dürfte somit technisch viel schwieriger zu erreichen sein – und demzufolge vermutlich einen (deutlich) längeren Zeitraum bis zur finalen Spezifikation benötigen.

Verwandte News

- Umfrage-Auswertung: Welche neue Hardware wird im Jahr 2022 am meisten erwartet?

- Neuer Artikel: Das Hardware-Jahr 2022 in der Vorschau

- Umfrage-Auswertung: Welche neue Hardware wird im Jahr 2021 am meisten erwartet?

- Neuer Artikel: Das Hardware-Jahr 2021 in der Vorschau

- Neuer Artikel: Das Hardware-Jahr 2020 in der Vorschau

- Gerüchteküche: Das vierte Quartal 2022 soll Zen 4, RDNA3, Lovelace & Raptor Lake bringen

- Umfrage-Auswertung: Werden die Systemanforderungen für die Spiele-Generation 2020/21 erfüllt?

- Neuer Artikel: Die Systemanforderungen für die Spiele-Generation 2020/21

- AMD verschiebt Zen 3 angeblich auf Anfang 2021

- Umfrage-Auswertung: Werden die Systemanforderungen für die Spiele-Generation 2019/20 erfüllt?