Hauptlinks

Suchen

Intels Haswell-Architektur mit eingebettetem DRAM?

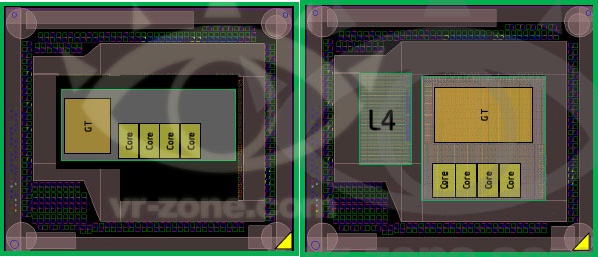

Die VR-Zone berichtet über die 2013er CPU-Architektur "Haswell" seitens Intel und zeigt diesbezüglich Die-Symbolbilder, welche das Haswell-Die (rechts) im Vergleich zum Ivy-Bridge-Die (links) darstellen sollen. Dabei wurden (von Intel?) weitere Informationen eingezeichnet, so daß man zum einen die CPU-Rechenkerne als auch die integrierte Grafiklösung erkennen kann – und bei Haswell zudem einen als "L4" bezeichneten extra Bereich bzw. sogar ein extra Die auf dem Trägermaterial. Daraus schließt die VR-Zone auf das Vorhandensein eines Level4-Caches bei Haswell – die dafür gesetzte Bezeichnung "L4" unterstützt dies natürlich, auch wenn ein Level4-Cache im Sinne dieser Mainstream-CPU eigentlich als wenig sinnvoll erscheint. Die wahrscheinlichere Auflösung ist hierbei die Verwendung von eingebettetem DRAM, welcher zuerst einmal der integrierten Grafikeinheit zur Verfügung steht und dann als Zweitverwertung noch als Level4-Cache funktionieren könnte.

Eine solche Idee hatte Intel schon des längerem für Haswell, um das typische Problem von Mainstream-CPUs mit immer leistungsfähigeren integrierten Grafiklösungen zu bekämpfen, welche jedoch bei der Speicherbandbreite auf immer das gleiche Speicherinterface (Dual 64 Bit DDR) und derzeit immer noch dieselbe Speichersorte (DDR3) mit deren bekannten Taktraten limitiert sind. Insbesondere bei für den Mainstream-Markt gedachten Prozessoren wie auch AMDs Llano und Trinity ist dieses Problem auch nicht mit noch größeren Speicherinterfaces (wie bei echten Grafikkarten) zu lösen, weil diese größeren Speicherinterfaces im Sinne der CPU-Leistung im Mainstream-Bereich nahezu nutzlos sind, dafür aber deutlich höhere Kosten auf Mainboard-Seite verursachen und damit einen erheblichen Nachteil im preissensitiven OEM-Geschäft darstellen.

Ein eingebetteter DRAM löst diese Probleme, da eine gewisse Speichermenge sehr schnell an den integrierten Grafikchip angebunden werden kann, der restliche Grafik-Speicher wird dann wie gehabt über den (gesharten) PC-Hauptspeicher zur Verfügung gestellt. Beispielsweise die Xbox 360 verfügt bereits über ein solches Modell, dort wurden dem ATI-Grafikchip 10 MB eDRAM zur Verfügung gestellt – im übrigen anfänglich ebenfalls als extra Die auf dem Trägermaterial. Wieviel eDRAM es bei Haswell werden, ist unklar – vor allem, da die auf dem Symbolbild dafür eingezeichnete Chipfläche durch die Verwendung von stacked DRAM keinen Hinweis auf die tatsächlich zur Verfügung stehende Chipfläche für den eDRAM darstellt (mittels stacked DRAM können mehrere Lagen an DRAM übereinander gestappelt werden). Hinzu kommt der Punkt, daß der eingebettete Speicher bei Haswell natürlich ein extra Die darstellt, welches auch extra hergestellt wird – unter Umständen in einem ganz anderem Fertigungsverfahren als der restliche Haswell-Chip (22nm bei Intel).

Die Ausführung als extra Die ermöglicht es Intel natürlich in erster Linie, den eingebetten Speicher nur dort zu verbauen, wo man diesen auch wirklich benötigt – dies gilt ganz sicher nicht bei Prozessoren-Modellen, wo nur eine kleinere Grafikeinheit geboten wird. Zudem wäre es auch möglich, unterschiedliche Größen dieses eingebetteten Speichers anzubieten, je nach Performance-Profil des jeweiligen Prozessoren-Modells. Dies verhindert, daß Intel bei Billigmodellen wie der Pentium-Serie durchgehend höhere Kosten hat – die höheren Kosten treten dann nur dort auf, wo Intels dies wünscht bzw. wo es sich aufgrund des höheren Abgabepreises auch lohnt. Dafür bedeutet diese Methode der zwei Dies aber natürlich einen gewissen höheren Aufwand, weil dann eben die zwei Dies auf dem Trägermaterial mittels eines hochbandbreitigen extra Interfaces miteinander verbunden werden müssen.

| Sandy Bridge | Ivy Bridge | Haswell | |

|---|---|---|---|

| Fertigung | 32nm bei Intel | 22nm bei Intel | 22nm bei Intel |

| Chipfläche (4C-Die) | 216mm² | ~170mm² | ~210mm² |

| Chipfläche der integrierten Grafik (4C-Die) | ca. 40mm² | ~35mm² | ~75mm² |

| Recheneinheiten der integrierten Grafik (4C-Die) | 12 EU (DirectX 10.1) |

16 EU (DirectX 11) |

angeblich 40 EU (DirectX 11.1) |

| eingebetter Speicher | - | - | ~65mm² extra Die |

Davon abgesehen zeigen die Die-Symbolbilder noch (sofern sie bezüglich der eingezeichneten Größen halbwegs korrekt sind), daß das Haswell-Die außerhalb des eDRAM ca. ein Viertel größer ist als daß Ivy-Bridge-Die. Haswell sollte also bei einer Chipfläche von ca. 210mm² herauskommen, nachdem Ivy Bridge derzeit auf ca. 170mm² geschätzt wird – Intel nutzt also bei Haswell die Möglichkeiten der 22nm-Fertigung dann stärker aus und kommt auf eine Chipfläche ähnlich wie bei Sandy Bridge (216mm² unter 32nm). Dabei wächst die integrierte Grafik zwischen Ivy Bridge und Haswell um satte ca. 115% – an dem früheren Gerücht, Intel würde bei der integrierten Haswell-Grafik bis zu 40 Recheneinheiten verbauen, könnte also durchaus etwas dran sein. Zumindest scheint eine weitere Verbesserung der integrierten Grafik ganz offensichtlich ein Hauptpunkt der Haswell-Architektur zu sein – welche auf CPU-Seite bisher nur mit der Befehlssatzerweiterung AVX 2.0 eine klar benennbare Neuerung bringen wird.

Verwandte News

- Neuer Artikel: Launch-Analyse: Intel Haswell

- Nächster Haswell-Vorabtest bestätigt: Starke CPU-Performance nur bei AVX2 & FMA3

- Weiterer Haswell-Vorabtest zeigt maue CPU-, jedoch gute iGPU-Zugewinne an

- Intels Haswell-Grafik: Von HD Graphics bis "Iris Pro 5200"

- Intel verspricht eine Haswell-Grafikperformance auf Höhe der GeForce GT 640

- Erste umfangreiche Haswell-Benchmarks zeigen ca. 5% mehr Pro-MHz-Leistung an

- Neuer Artikel: Das Hardware-Jahr 2013 in der Vorschau

- Haswells Grafiklösung ist (angeblich) so schnell wie eine GeForce GT 650M

- Aktualisierte Performance- & Preis-Übersicht AMD Llano & Trinity vs. Intel Core i3 & Pentium G

- Aktualisierte Performance-Einordnung integrierter Desktop-Grafiklösungen