Hauptlinks

Suche

Spezifikationen der drei Turing-Chips TU102, TU104 & TU106 offengelegt

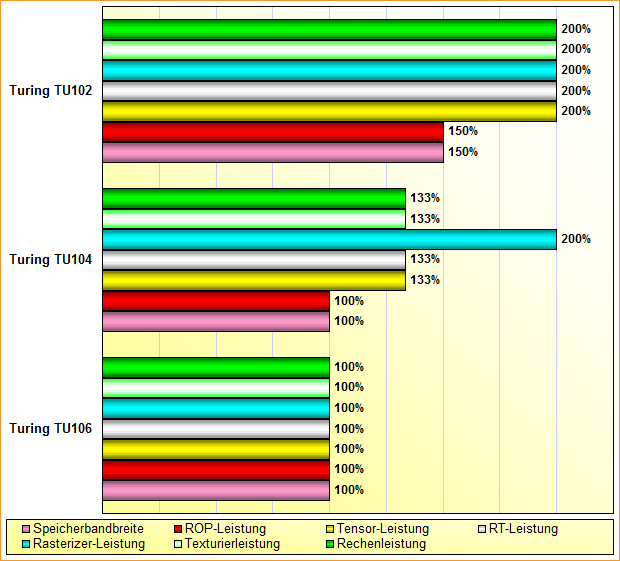

Bei Videocardz hat man Zugang zu einem "nVidia Turing Architecture White Paper" und zitiert hieraus interessante Details zur anstehenden Turing-Generation. Markant hierbei ist vor allem die echte Offenlegung der drei Turing-Chips TU102, TU104 und TU106, was bei der Turing-Vorstellung nur ziemlich lückenhaft abgehandelt wurde. Die Turing-Chips TU102 & TU104 waren zwar schon ziemlich weit ausgebreitet, der TU106 kommt nun noch hinzu – mit einer kleinen Überraschung in dieser Form, als das jener Grafikchip tatsächlich den Unterbau der GeForce RTX 2070 darstellen wird. Damit bringt nVidia gleich drei sehr große Chips daher, welche sich bei den Chipflächen ungewöhnlich gering unterscheiden – der TU102 (754mm²) ist nur +38% größer als der TU104 (545mm²) und der TU104 gar nur +22% größer als der TU106 (445mm²). Insbesondere TU104 und TU106 trennen somit nur 100mm² Chipfläche, was selbst angesichts des hohen Performancelevels der damit herauskommenden Grafikkarten vergleichsweise wenig ist.

| TU106 | TU104 | TU102 | |

|---|---|---|---|

| Chip | 10,6 Mrd. Transistoren auf 445mm² Chipfläche in der 12nm-Fertigung von TSMC | 13,6 Mrd. Transistoren auf 545mm² Chipfläche in der 12nm-Fertigung von TSMC | 18,6 Mrd. Transistoren auf 754mm² Chipfläche in der 12nm-Fertigung von TSMC |

| Hardware | 3 Raster-Engines, 36 Shader-Cluster, 2304 Shader-Einheiten, 144 TMUs, 36 RT-Cores, 288 Tensor-Cores, 64 ROPs, 4 MB Level2-Cache, 256 Bit GDDR6-Speicherinterface | 6 Raster-Engines, 48 Shader-Cluster, 3072 Shader-Einheiten, 192 TMUs, 48 RT-Cores, 384 Tensor-Cores, 64 ROPs, 4 MB Level2-Cache, 256 Bit GDDR6-Speicherinterface | 6 Raster-Engines, 72 Shader-Cluster, 4608 Shader-Einheiten, 288 TMUs, 72 RT-Cores, 576 Tensor-Cores, 96 ROPs, 6 MB Level2-Cache, 384 Bit GDDR6-Speicherinterface |

| NVLink & SLI | - | ein NVLink 2.0 x8-Anschluß (50 GB/sec), Support für maximal 2fach SLI | zwei NVLink 2.0 x8-Anschlüsse (100 GB/sec), Support für maximal 2fach SLI |

| verbaut bei | GeForce RTX 2070 (Vollausbau) | GeForce RTX 2080 (Salvage) & Quadro RTX 5000 (Vollausbau) | GeForce RTX 2080 Ti (Salvage) & Quadro RTX 6000/8000 (Vollausbau) |

Augenscheinlich ist dies für nVidia aber dennoch wirtschaftlich – wahrscheinlich bedingt durch die absolut gesehen großen Chipflächen, wo andere Regeln als bei kleineren Chips gelten. Immerhin ist der TU106 mit seinen 445mm² Chipfläche selbst schon ein vergleichsweise großer HighEnd-Chip, selbst wenn die "xx6" im Codename eigentlich auf einen Midrange-Chip mit üblicherweise 200-250mm² Chipfläche hindeuten würde. Interessant ist an der konkreten Hardware der einzelnen Turing-Chips noch der Punkt, das nVidia dem TU104-Chip ungewöhnlicherweise gleich 6 Raster-Engines mitgegeben hat – die doppelte Anzahl wie beim TU106-Chip und damit exakt auf dem Niveau des TU102-Chips. Dies ergibt ein ungleiches Verhältnis zwischen Shader-Clustern und Raster-Engines bei diesem TU104-Chip, welcher somit nur 8 Shader-Cluster pro Raster-Engine versorgen muß, nicht gleich 12 Shader-Cluster pro Raster-Engine wie bei TU102 & TU104 (sowie den vorhergehenden Pascal-Chips). Die passendere Anzahl an Raster-Einheiten beim TU104-Chips wären somit eigentlich 4 (und nicht 6) gewesen – wieso nVidia sich zu dieser Änderung entschlossen hat, welche ja auch noch Chipfläche kostet, wäre interessant einmal erklärt zu bekommen.

Nichtsdestotrotz bleibt der TU106-Chip vergleichsweise (sehr) nahe dran am TU104-Chip dran, trägt ersterer immerhin 75% von dessen Shader-Einheiten beim identischen Speicherinterface. Letzteres hätte nVidia sicherlich gern zugunsten einer kleineren Chipfläche abgespeckt, allerdings wäre man für ein 192-Bit-Interface samt daraus zwingend 6 GB Grafikkartenspeicher angesichts des Preispunkts der GeForce RTX 2070 glatt ausgelacht worden. Ob es neben diesen drei Turing-Chips später noch weitere Turing-Chips mit/ohne RayTracing geben wird, ergibt sich im übrigen aus den jetzt bekannt gewordenen Daten noch nicht, dürfte nVidia aber sicherlich sowieso erst (viel) später öffentlich machen wollen. Der mit der Turing-Architektur einhergehenden erhebliche Flächenzuwachs (der TU106-Chip ist mit 2304 Shader-Einheiten auf 445mm² deutlich größer als der GP104-Chip mit 2560 Shader-Einheiten auf 314mm²) macht es allerdings nicht gerade wahrscheinlich, das nVidia sich innerhalb der 12nm-Fertigung an weiteren Turing-Chips für niedrigere Performance-Segmente versucht – so viel Chipfläche zu verballern kann man sich eben nur bei hohen Preislagen leisten, eher weniger denn im (preislich limitierten) Mainstream- und Midrange-Segment.

Verwandte News

- nVidias Turing-Architektur bohrt die Shader-Cluster deutlich auf

- Die Grafikchip- und Grafikkarten-Marktanteile im zweiten Quartal 2018

- nVidias Pascal-Grafikkarten bleiben wohl bis mindestens Jahresende 2018 im Angebotsportfolio

- Turing-Midrangechip "TU106" für die GeForce RTX 2060 deutet sich an

- Die Benchmarks zur GeForce RTX 2080 kommen am 17. September, jene zur GeForce RTX 2080 Ti am 19. September

- Erster 3DMark13-Wert zur GeForce RTX 2080 Ti liegt um +36% besser als bei der GeForce GTX 1080 Ti

- Angeblicher Benchmark-Leak zeigt die GeForce RTX 2080 Ti um +37,5% vor der GeForce GTX 1080 Ti

- Umfrage-Auswertung: Produziert die Grafikkarte ein hörbares Fiepen (2018)?

- Erster 3DMark13-Wert zur GeForce RTX 2080 zeigt ein Performance-Niveau leicht besser als bei der GeForce GTX 1080 Ti an

- Auslieferungsplan zur GeForce RTX Serie aufgetaucht