Hauptlinks

Suchen

Die-Shot zu AMDs Fiji-Chip aufgetaucht

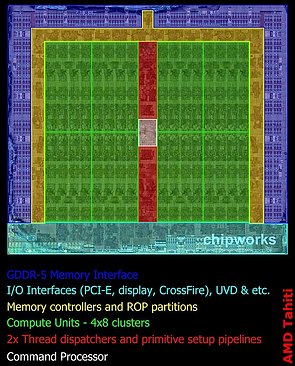

Der Teaser eines Reports der Chipanalysten von Chipworks beinhaltet einen ersten Die-Shot zu AMDs Fiji-Grafikchip der Radeon R9 Nano/Fury Serie. Die wirklich hochauflösenden, aufbearbeiteten und dann entsprechend markierten Die-Shots wird es sicherlich nur im vollständigen aka kostenpflichtigen Report geben, so daß wir derzeit vorerst mit diesem einen Die-Shot leben müssen. Einige Chip-Bestandteile sind dabei schon halbwegs identifizierbar – insbesondere wenn man es mit dem (markierten) Die-Shot zum Tahiti-Chip von Radeon HD 7900 und R9 280 Serien vergleicht:

AMD Fiji Die-Shot |

AMD Tahiti Die-Shot (markiert) |

Auf den ersten Blick könnte man denken, daß man aufgrund des Die-Shots eine Größenangabe zur Pad-Area des Speicherinterfaces bekommt (abzüglich Speichercontroller, ROPs und Level2-Cache), jenes soll schließlich bei einem HBM-Speicherinterface deutlich kleiner werden. Aber am Ende ist diese einfarbige Abbildung zu uneindeutig – je nachdem, wo man die Ränder der Pad-Area vermutet, kommt ein ~30mm² großes Speicherinterface oder ein ~60mm² großes Speicherinterface heraus. Ersteres wäre immer noch mehr als die Erwartungen von 15mm² bei einem 4096 Bit DDR HBM1-Interface – und letzteres sogar genauso groß wie das 384 Bit DDR GDDR5-Interfaces des Tahiti-Chips. Wirklich sicheres kann man hier leider noch nicht herauslesen, eventuell können sich die Experten in unserem Forum einen besseren Reim hierauf machen.

Nachtrag vom 5. November 2015

Zum Fall des Fiji Die-Shots wäre noch nachzutragen, daß AMD laut der Diskussion zur News in der Tat zum Launch der Radeon R9 Fury X die früheren Annahmen zum Flächenbedarf eines HBM-Speicherinterfaces offiziell korrigiert hat: Demzufolge soll das 4096 Bit DDR HBM1-Interfaces des Fiji-Chips tatsächlich nur etwas kleiner ausfallen als das 512 Bit DDR GDDR5-Interfaces des Hawaii-Chips (früher geschätzt auf ~55mm²). Gedeckt wird diese Aussage durch eine genauere Ausarbeitung seitens WCCF Tech bezüglich jenes Fiji Die-Shots, bei welcher herauskam, daß ein 1024 Bit DDR HBM1-Interface in der Praxis etwas größer ist als ein 64 Bit DDR GDDR5-Interface von Tonga. Da AMDs Hawaii-Chip gleich acht dieser Interfaces hat, der Fiji-Chip aber nur vier HBM-Interfaces, würde das sogar einen Flächenvorteil des insgesamten HBM-Interfaces von 40% ergeben. Aber wie gesagt ist der Die-Shot nicht eindeutig genug, um hierzu endgültige Aussagen fällen zu können – ohne daß entweder hochauflösende Die-Shots vorliegen oder/und die echten Experten drübergeschaut haben.

Verwandte News

- GDDR5X-Speicher ist nunmehr offiziell spezifiziert

- HBM2-Speicher ist nunmehr offiziell spezifiziert

- HBM2-Speicher deutlich flexibler bei den Speichermengen und wahrscheinlich breit eingesetzt bei den 2016er Grafikchips

- Transistorenanzahl, Chipfläche und Packdichte früherer Spitzen-Grafikchips von AMD & nVidia

- Umfrage-Auswertung: Sind im Preisbereich 300-500€ Grafikkarten mit 8 GB interessant?

- Was bringen 4 GB bei der Radeon R9 380?

- Speicherübertaktung auf der Radeon R9 Fury X bringt interessante Rohleistungsgewinne

- 20nm- und 16nm-Fertigung von Grafikchips um einige Monate verschoben

- Umfrage-Auswertung: Wieso mehr als 4 GB Grafikkartenspeicher?

- Umfrage-Auswertung: Wieviel Grafikkartenspeicher sind derzeit für einen Neukauf ideal?